# Dedicated Inter-FPGA Networks for Scalable Reconfigurable Computing

**Kentaro Sano**

**RIKEN** Center for Computational Science (R-CCS)

## **Introduce Myself: Kentaro Sano**

Hiring researchers:

R-CCS2105 or R-CCS2022

Riken Center for Computational Science

#### **RIKEN Center for Computational Science**

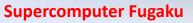

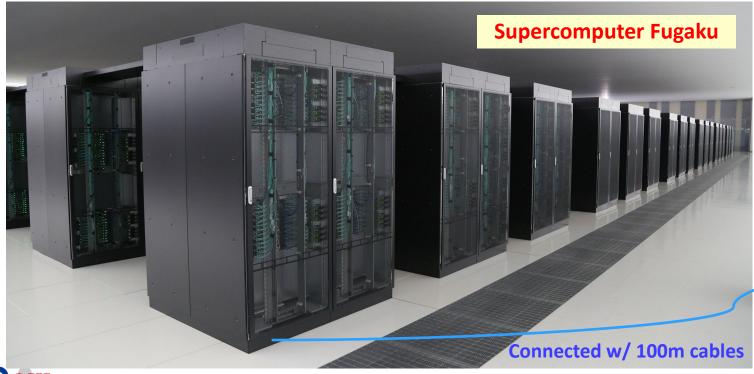

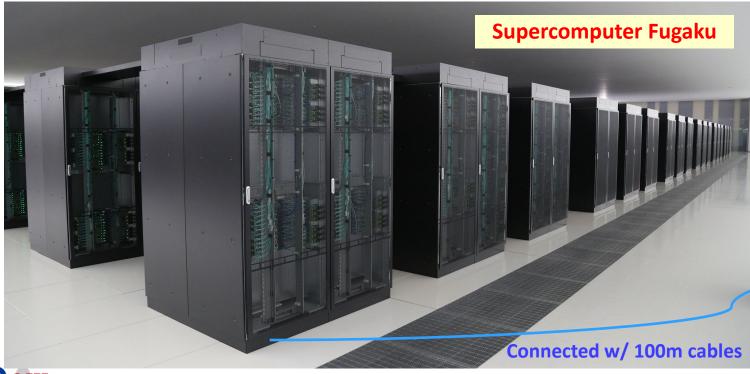

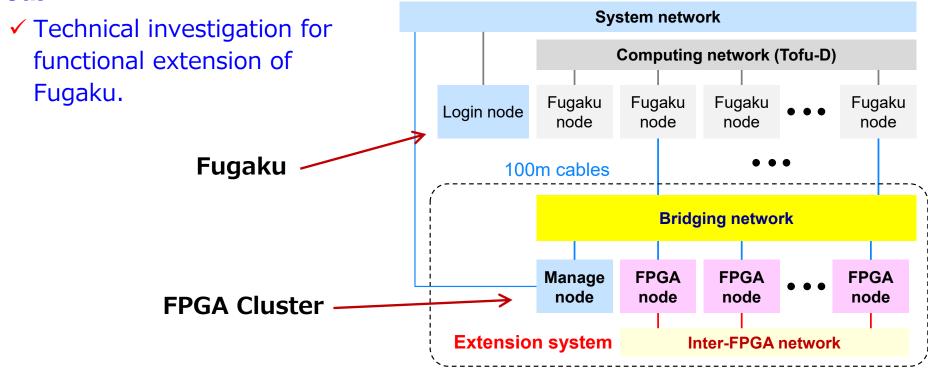

- ✓ Develop and operate Supercomputer Fugaku

- ✓ Facilitate leading edge infrastructures for research based on supercomputers

- ✓ Conduct cutting-edge research on HPC

#### Leader, Processor Research Team

- ✓ Exploration of future HPC architectures

- ✓ Advanced use of present HPC systems

#### Joint Laboratory at Tohoku University

✓ Visiting Professor "Advanced Computing Systems Lab"

## **Goal and Roadmap of Processor Research Team**

#### **Establish HPC architectures suitable for Post-Moore Era**

#### **Exploration of New HPC Architectures**

- ✓ Novel accelerators based on data-flow model (CGRA)

- ✓ System architectures

#### **Near-sensor / Near-storage Processing**

✓ FPGA-based processing for X-ray imaging detector

#### **Exploration for Novel Computing Principle**

Specialized hardware design for quantum error correction

## **Outline**

- Introduction

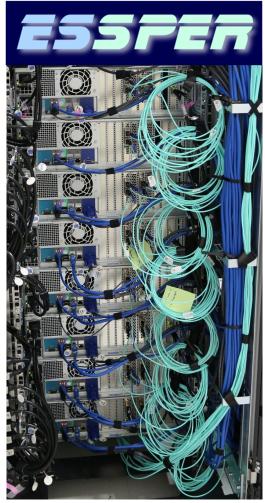

- **ESSPER**: FPGA Cluster Prototype

- Inter-FPGA network

- Implementation and evaluation

- Conclusions

**ESSPER: FPGA Cluster System**

### Introduction

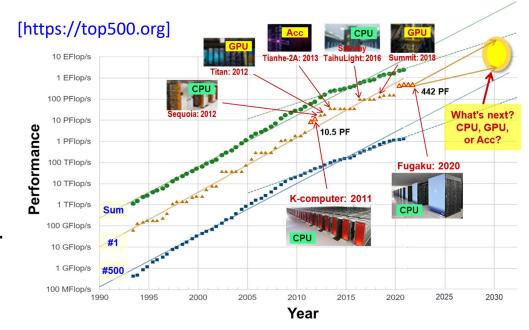

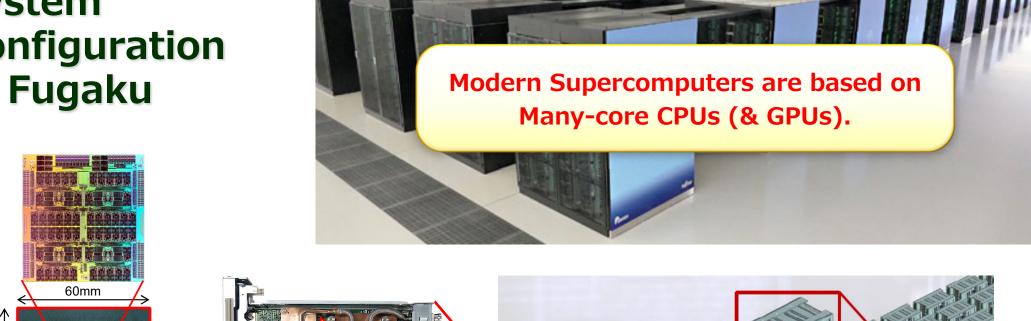

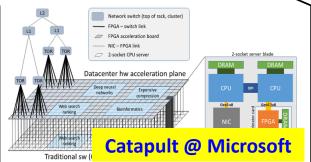

#### Accelerators for higher power-efficiency

- ✓ System power is the most critical issue.

(Fugaku: 20+MW for operation, 30MW as max.)

- ✓ Standard CPUs are not sufficient. Accelerators (Accs) for higher performance per power.

#### Reconfigurable computing with FPGAs

- ✓ GPUs are popular as gen-purpose Accs.

- ✓ More specialized, higher efficiency. But we also need flexibility. FPGAs!

#### Prototype FPGA Cluster "ESSPER"

- ✓ Proof-of-concept system to evaluate FPGA-based extension of Fugaku.

- ✓ Challenges:

How to scale with multiple FPGAs

## **Motivation and Objective**

#### Motivation

- ✓ What kind of inter-FPGA network are appropriate?

- ✓ Assumption: Many FPGAs in a system.

Each of users uses them partially.

#### Objective

## Find inter-FPGA network appropriate for a large-scale system with multiple users

- ✓ Investigate requirements

- ✓ Compare Direct and Indirect networks

- ✓ Propose Virtual circuit-switching network (VCSN)I

- ✓ Design, implement, and evaluate

# **ESSPER:** FPGA Cluster Prototype

## Elastic and Scalable System for High-Performance Reconfigurable Computing

**Experimental prototype for research on functional extension with FPGAs**

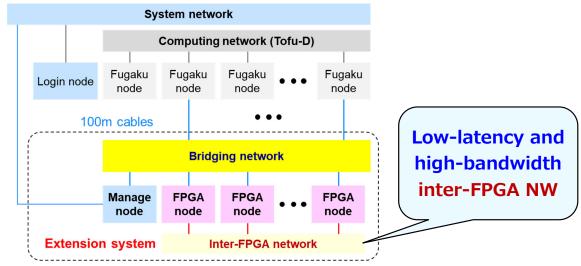

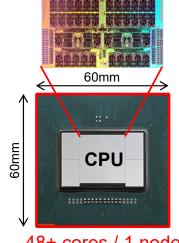

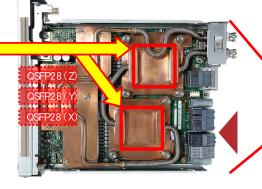

## **System** Configuration of Fugaku

48+ cores / 1 node 2.7+ TF

2 nodes **CPU-Memory** 5.4+ TF Unit (CMU)

BoB Shelf 48 nodes

16 nodes 43+ TF 129+ TF Rack

384 nodes 1+ PF

Fugaku

158,976 nodes 537 PF @ FP64 (414 racks)

Sep 5, 2022

Photos & figs by Fujitsu

## Elastic and Scalable System for High-Performance Reconfigurable Computing

**Experimental prototype for research on functional extension with FPGAs**

# Elastic and Scalable System for High-Performance Reconfigurable Computing

### **Architecture of ESSPER**

#### **Goal**

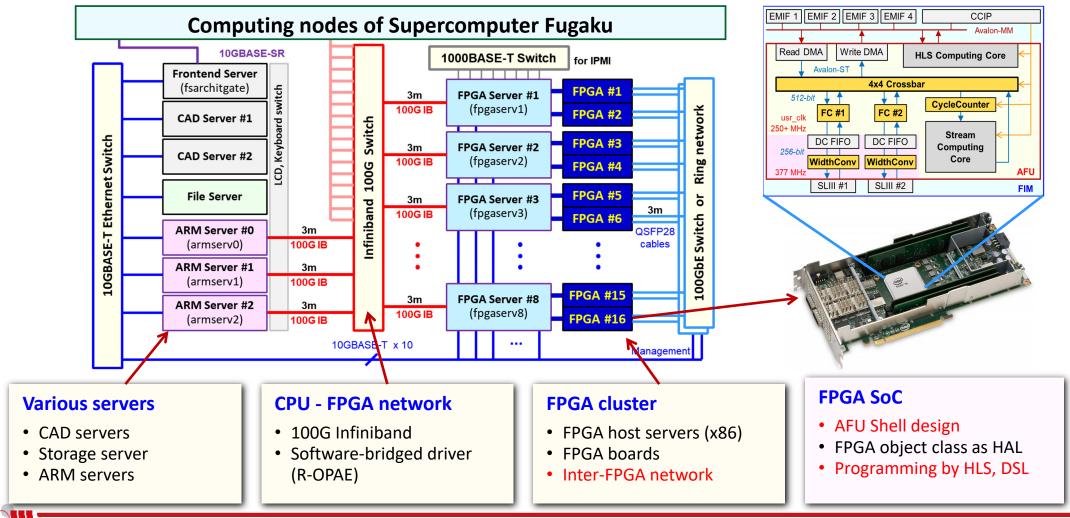

## **Hardware Organization of ESSPER**

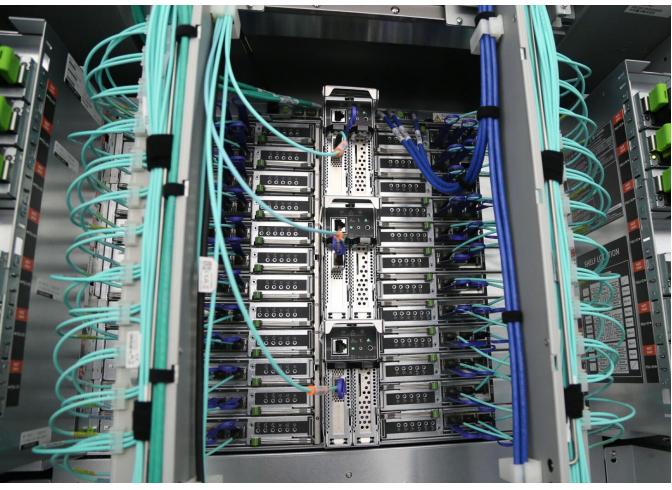

**FPGA SoC**

RIKEN R-CCS

## **Inter-FPGA Network**

## **Assumption and Requirements**

- A lot of FPGA resources in a system

- ✓ 100~, 1000~, or more?

- FPGAs are (globally or partially) connected by their dedicated networks

- ✓ Hardware programmed on multiple FPGAs operates by communicating and synchronizing with each other.

- Each of multiple users acquires a part of FPGAs and execute tasks on them.

- ✓ User A: 16 FPGAs with 2D torus network.

- ✓ User B: 64 FPGAs with a tree network.

## **Two Types of Networks**

|                 | Direct network                                             | Indirect network                                                      |  |

|-----------------|------------------------------------------------------------|-----------------------------------------------------------------------|--|

|                 | FPGA WRIR E FPGA                                           | Switches  MAC MAC FPGA  FPGA FPGA  FPGA FPGA  FPGA  FPGA  FPGA        |  |

| Characteristics | p2p-connection without switches,<br>typical: torus network | connection with switches,<br>typical: Ethernet                        |  |

| Switching       | circuit or packet (w/ on-chip router)                      | packet                                                                |  |

| Pros            | low latency,<br>easy to use with simple HW                 | flexibility, small diameter, easy adoption of cutting-edge            |  |

| Cons            | large diameter, inflexibility in resource allocation       | higher latency due to packet processing, complex and difficult to use |  |

## Related Work: Networks for FPGAs in HPC/DC

| Туре            | Direct network                                  | Indirect network                               | Indirect circuit-switching nw         |

|-----------------|-------------------------------------------------|------------------------------------------------|---------------------------------------|

| Characteristics | p2p-connection without switches, typical: torus | connection with switches,<br>typical: Ethernet | connection with optical switch (MEMS) |

| Switching       | circuit or packet (w/ router)                   | packet                                         | circuit or packet (w/ router)         |

| Pros            | low latency                                     | flexibility, small diameter                    | low latency, flexibility              |

| Cons            | inflexibility, large diameter                   | higher latency, complex                        | expensive, signal attenuation         |

#### **Representative systems**

## What Network is Appropriate for Multi-User System?

#### Inflexibility of direct network

- Cannot provide requested topology for partial use of FPGAs

- ✓ Full torus cannot be provided.

Only (n-1)-D torus or mesh available

#### Flexibility of indirect network

- Can provide any topology for any part of the FPGA nodes

- ✓ Appropriate for operation of a large system with multiple users

- ✓ However, complicated to use due to packet generation and destination control

#### **Example of 2D torus network.**

Partial usage is limited to 1D torus or 2D mesh.

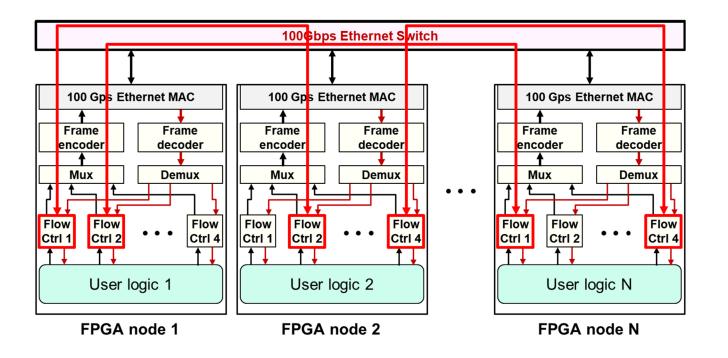

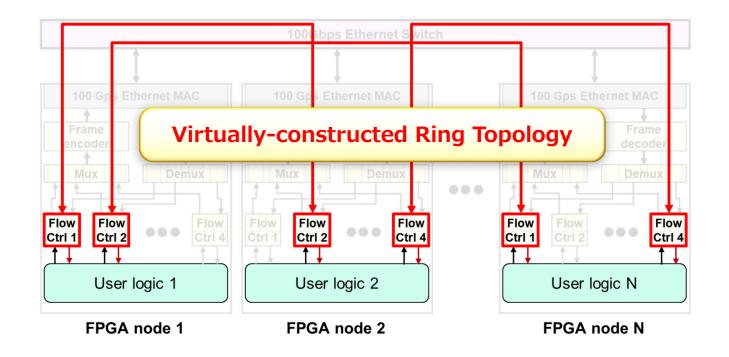

## Proposal: Virtual Circuit Switching Network (VCSN)

#### Provide arbitrary topology with virtual links over Ethernet

✓ Easy to use by simply sending data through a virtual topology.

No complex control required for user logic.

## Proposal: Virtual Circuit Switching Network (VCSN)

#### **Provide arbitrary topology with virtual links over Ethernet**

✓ Easy to use by simply sending data through a virtual topology.

No complex control required for user logic.

## Mechanism of Virtual Circuit-Switching

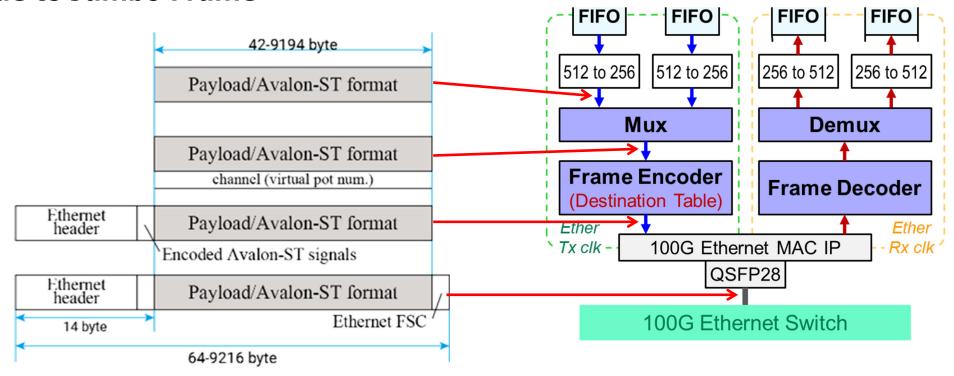

## Payload Efficiency of VCSN

Theoretical max efficiency: 99.54% due to Jumbo Frame

Ethernet FCS: Frame Check Sequence

## **Implementation and Evaluation**

### FPGA Shells for Direct and Indirect Networks

#### **Direct connection network (DCN)**

#### PCIe gen3 x16 (15.75 GB/s) DDR4 Memories (19.2 GB/s x 4) EMIF 2 EMIF 3 EMIF 4 CCIP Avalon-MM Write DMA Read DMA **HLS Computing Core** Avalon-ST 4x4 Crossbar 512-bit CycleCounter FC #2 FC #1 usr clk 250+ MHz Stream DC FIFO DC FIFO Computing 256-bit Core WidthConv WidthConv 377 MHz **AFU** SLIII #1 SLIII #2 FIM QSFP28 (12.5 GB/s x 2) 100G SerialLite3 with flow controller (FC) Another FPGA board Another FPGA board

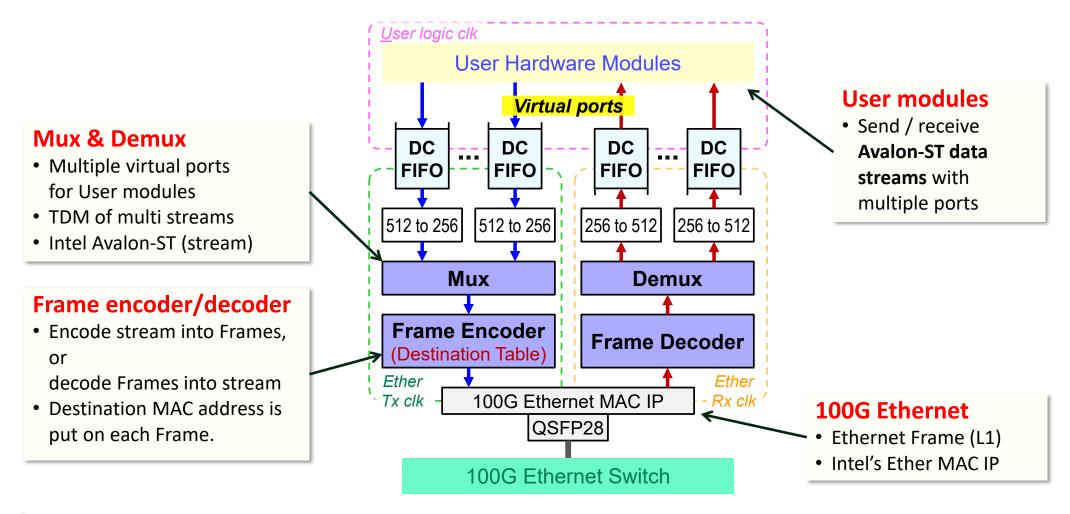

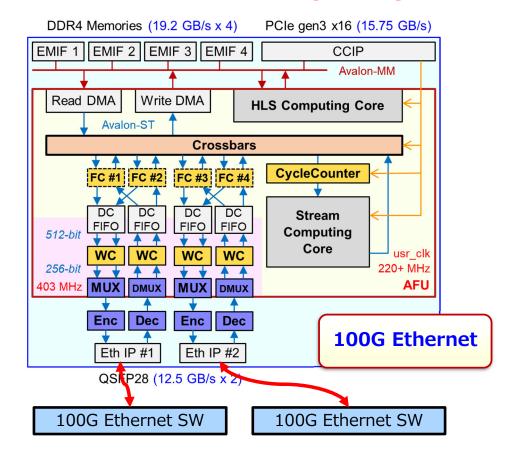

#### **Indirect network (VCSN)**

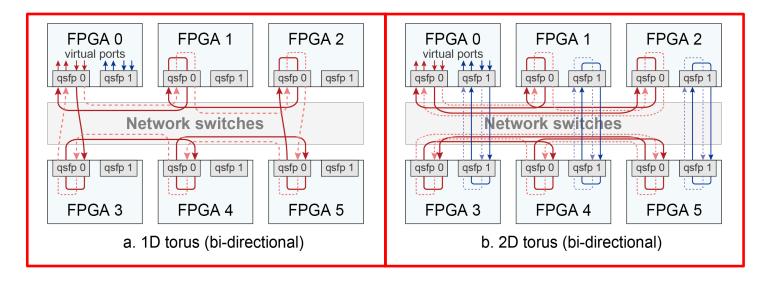

## VCSN Setup with 100Gbps Ethernet Switches

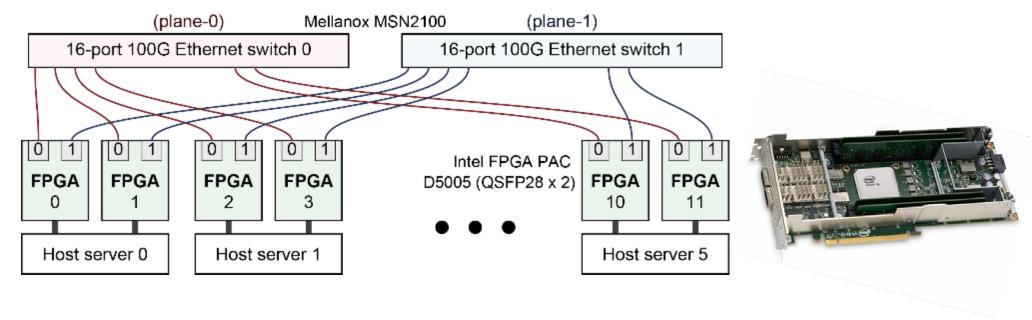

#### **Intel PAC D5005 FPGA cluster with VCSN**

- Two 16-port 100G Ethernet switches

- Two ports of FPGA are connected to a different switch (Dual Plane).

Tomohiro Ueno, Atsushi Koshiba, Kentaro Sano, "Virtual Circuit-Switching Network with Flexible Topology for High-Performance FPGA Cluster," Procs. of ASAP, pp.41-48, 2021.

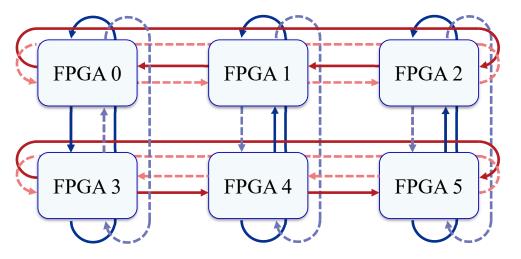

## VCSN Configuration Examples

6-FPGA networks

- 1-D torus

- 2-D torus (2x3)

Virtual topology of bi-dir 2D Torus

Tomohiro Ueno, Atsushi Koshiba, Kentaro Sano, "Virtual Circuit-Switching Network with Flexible Topology for High-Performance FPGA Cluster," Procs. of ASAP, pp.41-48, 2021.

## **Area and Latency**

#### Area

#### DCN subsystem

|                      | ALM     | Registers | M20k  | DSP   |

|----------------------|---------|-----------|-------|-------|

| SL3                  | 10474.2 | 10356     | 18    | 0     |

| Width converter      | 1275.4  | 3626      | 0     | 0     |

| Flow controller      | 1175.1  | 1452.4    | 80    | 0     |

| Network<br>subsystem | 12924.7 | 15434.4   | 98    | 0     |

| Percentage           | 0.47%   | 0.14%     | 0.84% | 0.00% |

| Stratix 10 SX280     | 2753000 | 11012000  | 11721 | 5760  |

#### VCSN subsystem

|                   | ALM     | Registers | M20k  | DSP  |

|-------------------|---------|-----------|-------|------|

| 100G MAC          | 22884.3 | 24922     | 0     | 0    |

| MUX/DEMUX         | 9145.2  | 21458     | 28    | 0    |

| Encoder/decoder   | 32818.6 | 43577     | 84    | 0    |

| FIFO              | 2327.9  | 2336      | 832   | 0    |

| Width converter   | 1275    | 3626      | 0     | 0    |

| Network subsystem | 68451.4 | 95919     | 944   | 0    |

| Percentage        | 2.49%   | 0.87%     | 8.05% | 0%   |

| Stratix 10 SX280  | 2753000 | 11012000  | 11721 | 5760 |

#### latency (minimum)

| Network | path                          | latency [ns] |

|---------|-------------------------------|--------------|

| VCSN    | virtual ports ⇔ virtual ports | 851.093      |

| DCN     | Cable link                    | 243.137      |

|         | Crossbar ⇔ crossbar           | 490.942      |

Area and latency: DCN << VCSN

Tomohiro Ueno, Atsushi Koshiba, Kentaro Sano, "Virtual Circuit-Switching Network with Flexible Topology for High-Performance FPGA Cluster," Procs. of ASAP, pp.41-48, 2021.

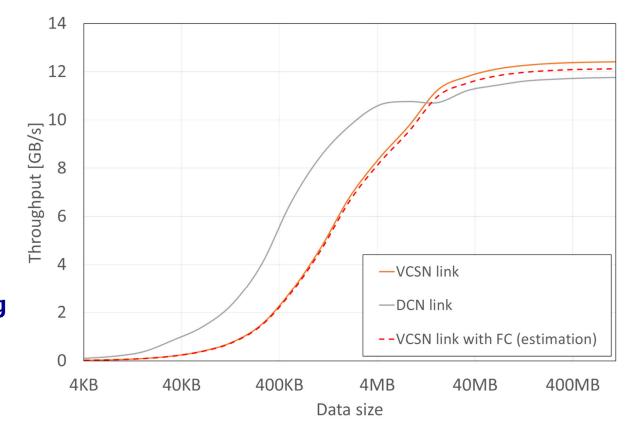

## Throughput (point-to-point)

## Throughput of VCSN rises slowly due to higher latency.

- ✓ P2P latency of VCSN 851 ns

- ✓ P2P latency of DCN 490 ns

#### VCSN has higher Max throughput.

- ✓ 100Gbps = 12.5 GB/s

- ✓ Jumbo frame of Ethernet is more efficient : 96% of the peak

Latency-tolerant stream computing should work well.

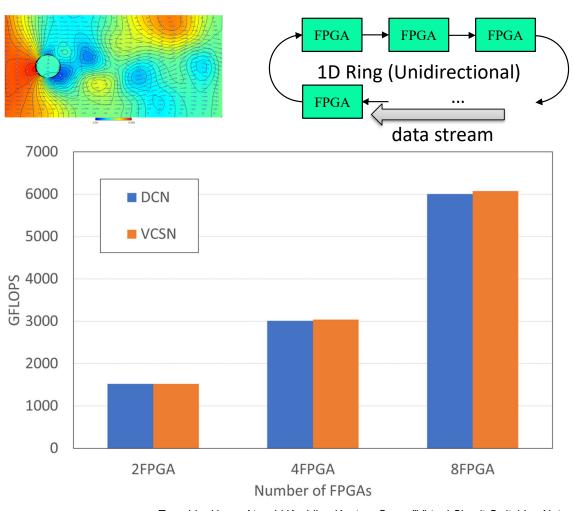

## Comparison of Stream-Computing Performance

#### 2D Fluid dynamics simulation

- ✓ Lattice Boltzmann method

- √ 48 PEs / FPGA, 155 MHz

- ✓ Streaming 2 GB test data

#### FLOPS by DCN ≒ FLOPS by VCSN

When bandwidth determines computational performance, **VCSN** is equivalent to DCN for a large data.

Tomohiro Ueno, Atsushi Koshiba, Kentaro Sano, "Virtual Circuit-Switching Network with Flexible Topology for High-Performance FPGA Cluster," Procs. of ASAP, pp.41-48, 2021. NANDA Workshop Sep 5, 2022

## **Summary**

**Objective** Find inter-FPGA network appropriate for

a large-scale system with multiple users

Our proposal Indirect network with VCSN

Virtualized circuit-switching network over

Ethernet frame for higher flexibility

**Comparison** x2 latency with slightly higher throughput

compared to DCN (direct connection network)

#### **Future work**

- ✓ System software to configure VCSN (almost implemented)

- ✓ Evaluation with application cases

#### Hiring researchers:

R-CCS2105 or R-CCS2022