# Conduction Bottleneck in Silicon Nanochain Single Electron Transistors Operating at Room Temperature

Muhammad A. Rafiq<sup>1,6,7</sup>, Katsunori Masubuchi<sup>1</sup>, Zahid A. K. Durrani<sup>2,6</sup>, Alan Colli<sup>3</sup>, Hiroshi Mizuta<sup>4,6</sup>, William I. Milne<sup>5,6</sup>, and Shunri Oda<sup>1,6</sup>

Received October 31, 2011; accepted December 10, 2011; published online February 6, 2012

Single electron transistors are fabricated on single Si nanochains, synthesised by thermal evaporation of SiO solid sources. The nanochains consist of one-dimensional arrays of  $\sim$ 10 nm Si nanocrystals, separated by SiO<sub>2</sub> regions. At 300 K, strong Coulomb staircases are seen in the drain–source current–voltage ( $I_{ds}$ – $V_{ds}$ ) characteristics, and single-electron oscillations are seen in the drain–source current–gate voltage ( $I_{ds}$ – $V_{gs}$ ) characteristics. From 300–20 K, a large increase in the Coulomb blockade region is observed. The characteristics are explained using single-electron Monte Carlo simulation, where an inhomogeneous multiple tunnel junction represents a nanochain. Any reduction in capacitance at a nanocrystal well within the nanochain creates a conduction "bottleneck", suppressing current at low voltage and improving the Coulomb staircase. The single-electron charging energy at such an island can be very high,  $\sim$ 20 $k_B$  T at 300 K. © 2012 The Japan Society of Applied Physics

## 1. Introduction

Single-electron devices in silicon, where charge on a nanoscale "island" is controlled at the one-electron level using the "Coulomb blockade" effect, 1-15) are highly promising systems for the development of low electron number, low power, transistor and memory large-scale integrated (LSI) circuits. 16,17) The single electron transistors have also been fabricated in materials other than Si. 18,19) Practical application of these devices requires room temperature operation and therefore a large island singleelectron charging energy  $E_c = e^2/2C \gg k_B T = 26 \text{ meV}$ , where C is the total island capacitance and temperature  $T = 300 \,\mathrm{K}$ . In practice, this requires  $C \sim 1 \,\mathrm{aF}$  or less and island dimensions <10 nm, such that the island forms a quantum dot. Room-temperature single-electron transistors (SETs) with islands of this scale have been fabricated mainly using high-resolution electron beam (e-beam) lithography. 20,21) These include both single-island, double-tunnel junction<sup>20,22,23)</sup> and many island, multiple tunnel junctions (MTJ) devices. 21) Recent measurements on SETs with ultrasmall islands, with diameter down to ~2 nm, show roomtemperature single-electron oscillations in the drain-source current-gate voltage  $(I_{ds}-V_{gs})$  characteristics with very large peak-valley ratios,  $\sim$ 100 or greater. <sup>23–25)</sup> However, a "Coulomb staircase" in the drain-source current-voltage  $(I_{ds}-V_{ds})$  characteristics can be less well resolved. The devices may be defined by complex high-resolution lithography<sup>20-23)</sup> or alternatively, defined "naturally" by material growth techniques. Examples of the later approach include SETs fabricated using nanocrystalline Si thin films, where crystalline Si grains  $\sim 10-30\,\mathrm{nm}$  in diameter form charging islands. <sup>18,24,26)</sup> These techniques raise the possibility of control over the island morphology at the nanoscale by controlling growth parameters.

Recently, we have observed strong Coulomb staircases at room temperature in the MTJ formed by a single Si nanochain.<sup>27)</sup> The Si nanochains, prepared by thermal evaporation of SiO solid sources, <sup>28,29)</sup> consist of one-

dimensional arrays of  $\sim$ 10 nm diameter Si nanocrystals (SiNCs) separated by narrow SiO<sub>2</sub> regions. Here, the SiNCs form charging islands and the SiO2 regions form tunnel barriers. Nanochain synthesis allows the preparation of very large "bulk" quantities of MTJs and Si quantum dots. In these MTJs, both islands and tunnel barriers are naturallydefined in entirety. Furthermore, in contrast with nanocrystalline Si thin films, 18,24,25) variations in SiNC size and separation within the same nanochain are better controlled  $(\pm 16\% \text{ variation}).^{27}$  Other investigations of these systems include measurement of electron tunneling in ensembles of Si nanochains using in situ scanning electron microscopy,<sup>30)</sup> non-gaussian fluctuations in charge transport in Si nanochains,<sup>31)</sup> electrical breakdown of individual nanochains, 32) and a theoretical prediction of negative differential conductance with large peak to valley ratio.<sup>33)</sup> However, detailed mechanism for single-electron effects in the nanochains, and the possibility of gate-control, is unclear.

In this paper, we report the  $I_{ds}-V_{ds}$  and  $I_{ds}-V_{gs}$  characteristics of room-temperature SETs fabricated using single Si nanochains. At 300 K, strong Coulomb staircases with varying current step height are seen in the  $I_{ds}$ - $V_{ds}$  characteristics, and single-electron oscillations are seen in the  $I_{\rm ds}$ - $V_{\rm gs}$  characteristics. The temperature dependence of the Coulomb staircase from 300-20 K shows a large increase in the width of the Coulomb blockade region. The new experimental data sets presented here that were not present in ref. 27 consist of a temperature dependence of the  $I_{ds}-V_{ds}$ curves, arrhenius curve and single electron oscillations. We investigate these characteristics using single-electron Monte Carlo simulations of an MTJ where the gate capacitance  $C_g$ at the islands is significant compared to the tunnel junction capacitance C. Here, the effective capacitance  $C_{\rm eff}$  for islands within the MTJ is reduced due to the presence of the capacitive array on either side, strengthening the Coulomb staircase at 300 K. The corresponding singleelectron charging energy can be very large,  $E_c = e^2/2C_{\rm eff} \sim$  $0.3 \,\mathrm{eV} \sim 11 k_\mathrm{B} T$  at 300 K. Furthermore, we find that the

<sup>&</sup>lt;sup>1</sup> Quantum Nanoelectronics Research Centre, Tokyo Institute of Technology, Meguro, Tokyo 152-8552, Japan

<sup>&</sup>lt;sup>2</sup>Department of Electrical and Electronic Engineering, Imperial College London, South Kensington Campus, London SW7 2AZ, U.K.

<sup>&</sup>lt;sup>3</sup>Nokia Research Centre c/o Nanoscience Centre, Cambridge CB30FF, U.K.

<sup>&</sup>lt;sup>4</sup>Nanoscale Systems Integration Group, School of Electronics and Computer Science, University of Southampton, Southampton, SO17 1BJ, U.K.

<sup>&</sup>lt;sup>5</sup> Engineering Department, University of Cambridge, Cambridge CB3 0FA, U.K.

<sup>&</sup>lt;sup>6</sup> SORST JST (Japan Science and Technology Agency), Kawaguchi, Saitama 332-0012, Japan

<sup>&</sup>lt;sup>7</sup> Department of Chemical and Materials Engineering, Pakistan Institute of Engineering and Applied Sciences, 45650 Islamabad, Pakistan

essential features in our data may be explained by inhomogeneity in the MTJ, where the total capacitance at an island well within the MTJ is reduced. The higher charging energy associated with such an island (up to  $\sim\!20k_BT$  at 300 K) leads to a "bottleneck" in conduction, suppressing current at lower voltages and leading to larger current steps in the Coulomb staircase. The formation of the "conduction bottleneck" is the key finding of this paper and was not discussed in the ref. 27. Only experimental data for a device with eight junctions MTJ was taken from ref. 27 to discuss the formation of the conduction bottleneck in addition to new experimental data.

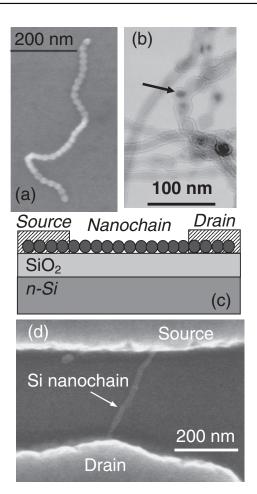

### 2. Device Fabrication

The Si nanochains were synthesised by thermal evaporation of high purity (99.99%) SiO powder solid source at 1400 °C, in a quartz tube furnace. <sup>28,29)</sup> Ar gas carried the vapour through the tube, and nanochains were synthesised in a cooler part of the furnace, at ~900 °C. Depending on growth conditions 10-50% nanowires may be present with the nanochains. The nanochains were undoped and consisted of SiNCs separated by SiO<sub>2</sub> "necks". Figure 1(a) shows a scanning electron micrograph of a nanochain. X-ray diffraction and high-resolution transmission electron microscopy indicated that SiNCs in the nanochain were crystalline. Figure 1(b) shows a high resolution transmission electron micrograph of nanochains dispersed on a copper grid from isopropyl alcohol (IPA) solution. The image is slightly under-focused to emphasise diameter variations. The SiNC diameter in different nanochains varies from <10 to  $\sim$ 30 nm. The SiNC marked with arrow has a diameter  $\approx$ 12 nm. A thin SiO<sub>2</sub> layer,  $\sim$ 1–3 nm thick, exists on the SiNCs outer surface. The widths of the necks vary from the diameter of the SiNCs to well below this value. The as-synthesised, sponge-like material was then dissolved in IPA (0.1 mg/3 ml) using ultrasonic tip agitation for 5 min, for spin-coating on suitable substrates.

Silicon nanochain SETs were fabricated using e-beam lithography to define contacts, using poly(methyl methacrylate) (PMMA) resist. Figure 1(c) shows a schematic diagram and Fig. 1(d) shows a scanning electron micrograph of a nanochain SET. Here, the Si substrate is used as a back-gate. The devices were defined on a  $\sim 100 \,\mathrm{nm}$  thick SiO<sub>2</sub> layer, grown thermally on a doped silicon substrate. The surface of the SiO<sub>2</sub> was treated with hexamethyldisilizane (HMDS) vapour for 3 min to promote adhesion. The nanochain solution was then spun onto the SiO<sub>2</sub> surface at 5000 rpm for 30 s to deposit nanochains on SiO<sub>2</sub>. Individual nanochains were then selected using scanning electron microscopy. Electrical contacts consisting of a 20 nm Ti/75 nm Al layer were then defined on individual nanochains using thermal evaporation. The source-drain contact separation defines the length of the nanochain segment, and the number of islands, in the device.

## 3. Experimental Results and Discussion

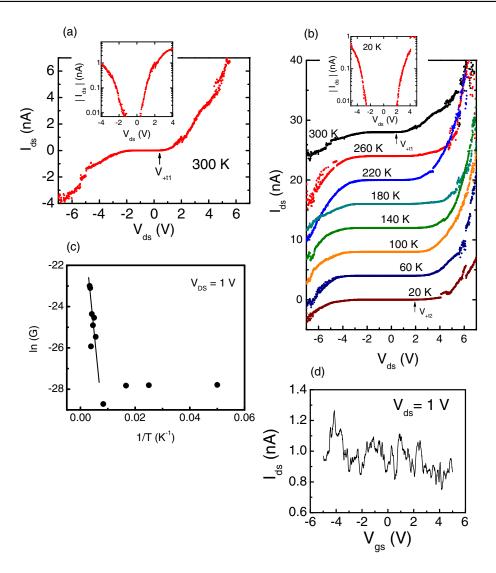

The nanochain SETs were electrically characterised in vacuum ( $\sim 10^{-6}$  mBar) using a low temperature probe station, BCT-43MDC from Nagase, and an Agilent B1500A semiconductor device analyser. Figure 2(a) shows the  $I_{\rm ds}$ - $V_{\rm ds}$  characteristics at 300 K from a device where the

**Fig. 1.** (a) Scanning electron micrograph of a Si nanochain deposited on SiO<sub>2</sub>. (b) Transmission electron micrograph of Si nanochains dispersed on a copper grid. (c) Schematic diagram of the silicon nanochain SET. (d) Scanning electron micrograph of a Si nanochain SET.

source–drain separation was  $\sim 150\,\mathrm{nm}$ , corresponding to a chain of 7 SiNCs at  $V_\mathrm{gs}=0$ . A Coulomb staircase characteristic is observed, with a low current "Coulomb gap" region at low voltage. The edges of the Coulomb gap are rounded due to thermally activated current. We extract threshold voltages for conduction  $V_{+t1}=0.4\,\mathrm{V}$  and  $V_{-t1}=-1.3\,\mathrm{V}$  by plotting the absolute value of the current on a log scale, to determine the onset of current [Fig. 2(a) inset]. We also see current steps in the characteristics outside the Coulomb gap, e.g., at  $\sim 2$  and  $\sim 3.6\,\mathrm{V}$ .

In our previous paper<sup>27)</sup> temperature dependence of  $I_{\rm ds}-V_{\rm ds}$  characteristics was not studied. Figure 2(b) shows the temperature dependence of the  $I_{\rm ds}-V_{\rm ds}$  characteristics, as the temperature is varied from 300–20 K, in steps of 40 K at  $V_{\rm gs}=0$ . The Coulomb gap increases as the temperature is reduced, with a large increase in the magnitude of the threshold voltages on both sides. For positive  $V_{\rm ds}$ , the threshold voltage increases in magnitude from  $V_{\rm +t1}=0.4\,\rm V$  at 300 K, to  $V_{\rm +t2}=2\,\rm V$  at 20 K [Figs. 2(a) and 2(b), insets]. For negative  $V_{\rm ds}$ , the threshold voltage decreases from  $V_{\rm -t1}=-1.3\,\rm V$  to  $V_{\rm -t2}=-2.6\,\rm V$ . The Coulomb gap is seen to increase greatly, from  $\sim$ 1.7 V at 300 K to  $\sim$ 4.6 V at 20 K. This increase is much larger than can be explained by the reduction in the thermally activated current around  $V_{\rm -t1}$  and  $V_{\rm +t1}$ .

Fig. 2. (Color online) (a)  $I_{\rm ds}-V_{\rm ds}$  characteristics of a nanochain SET at 300 K. The inset shows the data on a log-linear  $|I_{\rm ds}|-V_{\rm ds}$  plot at  $V_{\rm gs}=0$ . (b) Temperature dependence of the  $I_{\rm ds}-V_{\rm ds}$  characteristics for the same device at  $V_{\rm gs}=0$ . The inset shows the data at 20 K on a log-linear  $|I_{\rm ds}|-V_{\rm ds}$  plot. (c) Arrhenius plot of the logarithm of conductance G as a function of inverse temperature 1/T. (d) Current oscillations in the  $I_{\rm ds}-V_{\rm gs}$  characteristics of a second, similar nanochain device, at 300 K and  $V_{\rm ds}=1$  V.

Figure 2(c) shows an Arrhenius plot of the logarithm of conductance  $\ln G$  vs inverse temperature 1/T, measured at  $V_{\rm ds}=1\,\rm V.$   $V_{\rm ds}$  is chosen to correspond to  $>V_{+\rm t1}$  for current at 300 K. For temperatures from 300 to  $\sim$ 140 K (corresponding to inverse temperature 1/T from 0.0033 to 0.0071 K<sup>-1</sup>), the conductance decreases linearly as the thermally activated conductance falls, from 2.31 to 0.15 nS. This corresponds to an activation energy  $E_{\rm A}\sim 100\,\rm meV$ , and may be attributed to the highest charging energy in the SiNCs along the nanochain.<sup>34)</sup>

Single electron transistor oscillations were not discussed in our previous paper. Therefore we measured single electron oscillations in Si nanochain devices. Figure 2(d) shows current oscillations in the  $I_{\rm ds}$ – $V_{\rm gs}$  characteristics of a second, similar nanochain device at 300 K, at  $V_{\rm ds}=1$  V. The different device was used because the first device was damaged during the measurements. The oscillations are however weak, and do not show a single clear period. Any variation in the SiNC to back-gate capacitance along the MTJ would prevent the observation of single-period oscillations. Furthermore, the presence of traps along the

interface between the Si nanochain and the underlying, exposed SiO<sub>2</sub> surface would also degrade the oscillations. "Free energy" analysis<sup>34)</sup> suggests that Coulomb oscillations in an MTJ are periodic only for small deviations in the gate capacitance  $C_{\rm g}$ , with period  $e/\langle C_{\rm g} \rangle$ , where  $\langle C_{\rm g} \rangle$  is the average over all islands. This is not the case in our devices, suggesting large variation in  $C_{\rm g}$ .

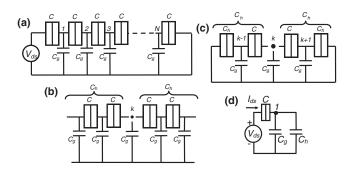

Our electrical characteristics may be associated with the formation of an MTJ along the nanochain. Figure 3(a) shows the circuit diagram of a homogenous N island MTJ, with the same tunnel junction capacitance C and the island-gate capacitance  $C_g$  along the MTJ. Looking from an island k well within the MTJ [Fig. 3(b)] at zero  $V_{\rm gs}$ , we may approximate the capacitive half-arrays on either side as semi-infinite, with capacitance  $C_{\rm h}$ . The "effective" capacitance seen from k is then  $C_{\rm eff} = C_{\rm g} + 2C_{\rm h}$ . Approximating half-arrays  $C_{\rm h}$  at islands k-1 and k+1, we also have  $1/C_{\rm h} = 1/(C_{\rm g}+C_{\rm h})+1/C$  [Fig. 3(c)] and rearranging this gives  $C_{\rm h} = (1/2)(\sqrt{C_{\rm g}^2+4CC_{\rm g}}-C_{\rm g})$ . Substituting  $C_{\rm h}$  into the expression for the effective capacitance gives us  $C_{\rm eff} = \sqrt{C_{\rm g}^2+4CC_{\rm g}}$ . We note that as  $C_{\rm h} < C$ ,  $C_{\rm eff} < C_{\rm t} = \sqrt{C_{\rm g}^2+4CC_{\rm g}}$ .

**Fig. 3.** (a) Multiple-tunnel junction model for an N island Si nanochain, with tunnel junction capacitance C and gate capacitance  $C_{\rm g}$ . (b) Multiple-tunnel junction approximation using Two semi-infinite capacitive arrays  $C_{\rm h}$  at islands k. (c) Multiple-tunnel junction approximation using capacitive arrays  $C_{\rm h}$  at islands k+1 and k-1. (d) Multiple-tunnel junction approximation looking from island 1.

$C_{\rm g}+2C$ , where  $C_{\rm t}$  is the total capacitance connected to the island. This increases the charging energy  $E_{{\rm c},k}=e^2/2C_{\rm eff}$  at island k in comparison with a single-island, double tunnel junction, and a corresponding increase in the MTJ SET operating temperature.

We next consider the effect of  $C_{\rm g}$  on the threshold voltage  $V_{\rm t}$ . Looking from the first island,  $C_{\rm h}$  lies in parallel with  $C_{\rm g}$  [Fig. 3(d)].  $V_{\rm ds}$  then causes a voltage  $V_{\rm l}=(C_{\rm g}+C_{\rm h})V_{\rm ds}/(C+C_{\rm g}+C_{\rm h})$  across the first junction. At the threshold voltage  $V_{\rm t}$ ,  $eV_{\rm l}$  is equal to the charging energy  $E_{\rm cl}=e^2/[2(C+C_{\rm g}+C_{\rm h})]$  and electrons are injected into the MTJ. This gives  $V_{\rm t}=e/[2(C_{\rm g}+C_{\rm h})]=e/(C_{\rm g}+C_{\rm eff})$ . If  $C_{\rm g}$  is negligible, then the island sees a one-dimensional (1D) array of capacitances C towards the right, with very small  $C_{\rm eff}$ . In consequence,  $E_{\rm cl}=eV_{\rm l}$  only at relatively high  $V_{\rm ds}$ , leading to a large value of  $V_{\rm t}$ . However, as  $C_{\rm g}$  increases, greater voltage drops across the first junction, lowering  $V_{\rm t}$ . For example, for  $C_{\rm g}=C$ ,  $C_{\rm h}=0.62C$  and  $V_{\rm l}=0.62V_{\rm ds}$ , i.e., the majority of applied voltage drops across the first junction.

We now consider the effect of an inhomogeneity in the MTJ. If the island k is poorly coupled to the gate, with a negligible value of  $C_{\rm g}$ , then  $C_{{\rm eff},k}\approx 2C_{\rm h}$  at k. This increases  $E_{{\rm c},k}=e^2/2C_{{\rm eff},k}$  relative to neighbouring islands and forms a conduction "bottleneck" along the MTJ. The increase in  $E_{{\rm c},k}$  raises the SET operation temperature relative to a homogenous MTJ, and further still relative to a double tunnel junction. However, a large variation in capacitance along the MTJ would prevent the observation of a single period single-electron oscillation. A similar bottleneck would also form if C is reduced at the island.

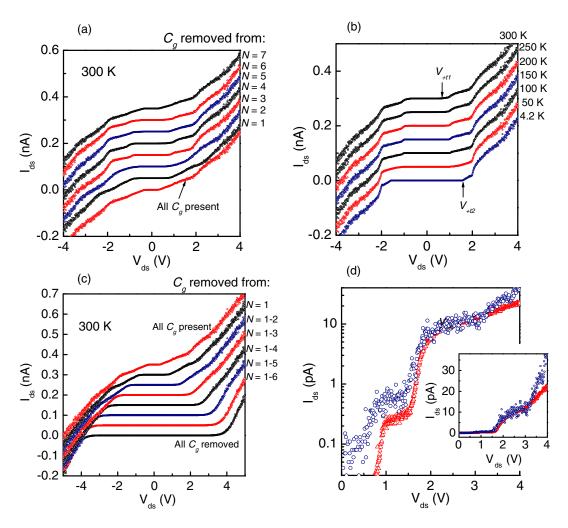

We now use single-electron Monte Carlo simulations<sup>35)</sup> of inhomogenous MTJs to explain qualitatively the essential features of our experimental data. We use an eight junction MTJ circuit, similar to the nanochain SET measured for Fig. 2. We also assume, for simplicity, equal tunnel junction capacitances C and gate capacitance  $C_g$  at all islands. We then remove  $C_g$  from one or more islands to form conduction "bottlenecks". Furthermore, as we observe a strong Coulomb staircase, asymmetry may also occur along the tunnel junctions. We include the effect of this by means of a random variation in the tunnel junction resistances  $R_n$ ,

reasonable given the variation in SiNC separation along the nanochain. There is also likely to be an associated variation in C, further increasing MTJ asymmetry and improving the Coulomb staircase. Small variations in the SiNC separation are likely to affect tunnel resistance more than tunnel capacitance. We neglect variation in C in our analysis for simplicity.

Figure 4(a) shows the simulated  $I_{ds}$ – $V_{ds}$  characteristics of the eight junction MTJ SET, as one gate capacitance at a time, from the first to the seventh island, is removed. Here, we use  $C = 0.12 \,\mathrm{aF}$ , and  $C_{\mathrm{g}} = 0.1 \,\mathrm{aF}$ , giving  $C_{\mathrm{eff}} = 0.24 \,\mathrm{aF}$ and  $V_{\rm t} = e/(C_{\rm g} + C_{\rm eff}) \approx 0.5 \, \rm V$ . Here, the corresponding value of  $E_c$  for a SiNC within the array is very large,  $E_{\rm c}=e^2/2C_{\rm eff}\sim 0.33\,{\rm eV},~\sim 12k_{\rm B}T$  at 300 K. The capacitance values are in the same range as those extracted for nanochain SETs in our previous work, 11) and correspond to the self capacitance of a sphere ~6 nm (sphere is in air) to  $\sim$ 1.5 nm (sphere embedded in SiO<sub>2</sub>) in diameter. These values then give the diameter of the conducting core in a SiNC. The average tunnel junction resistance  $R_{av} = 1 \text{ G}\Omega$ , with  $\pm 40\%$  variation in the resistances (0.6–1.4 G $\Omega$ ). For all  $C_{\rm g}$  present, the threshold voltage is small,  $V_{\rm t} \approx 0.3\,{\rm V}$  and the current steps are similar in height. If  $C_g$  is removed at one of the islands then  $V_{\rm t}$  increases, e.g.,  $V_{\rm t} \approx 0.7\,{\rm V}$  if  $C_{\rm g}$  is removed at the central (fourth) island. Our variation in  $V_t$ spans the range 0.3-0.7 V, and the experimental value of  $V_{+t1} = 0.4 \,\mathrm{V}$  at 300 K in Fig. 2(a) lies within this range. If  $C_{\rm g}$  is removed at the fourth island, at this island  $C_{{\rm eff},k} \approx$  $2C_{\rm h}=0.14\,{\rm aF}$ , a reduction compared to  $C_{\rm eff}=0.24\,{\rm aF}$ . This increases  $E_{c,k} = e^2/2C_{eff,k} = 0.57 \text{ eV} \sim 22k_BT$  at 300 K. This large value explains the clarity of single-electron effects in an inhomogeneous MTJ even at 300 K.

The second current step in Fig. 4(a) becomes more prominent if a given  $C_{\rm g}$  is removed, and the effect is strongest when  $C_{\rm g}$  is removed at the central island (step at  $V_{\rm ds}\approx 1.8\,\rm V$ ), implying greater influence of the "bottleneck". As the central island is the most isolated from the contacts, the contribution of  $C_{\rm g}$  to its charging energy is relatively large and removing  $C_{\rm g}$  has the strongest effect. For  $V_{\rm ds} > 1.8\,\rm V$ , the bottleneck charging energy is overcome and the current rises strongly. For  $V_{\rm ds} < 1.8\,\rm V$ , the bottleneck suppresses  $I_{\rm ds}$ , lowering the first step in current.

Figure 4(b) shows the temperature dependence of the simulated  $I_{\rm ds}$ – $V_{\rm ds}$  characteristics where  $C_{\rm g}$  is removed at the fourth island. As T reduces from 300–4.2 K, the thermally activated current below the second step falls ( $V_{\rm ds} < 1.8$  V). This leads to an increase in the observed threshold voltage, from  $V_{\rm t}=0.7$  V at 300 K to  $\sim$ 1.6 V at 4.2 K. The position of the second step does not change. This follows qualitatively the behaviour of the experimental data in Fig. 2(b), where the threshold voltage increases from  $V_{\rm +t1}=0.4$  V at 300 K, to  $V_{\rm +t2}=2$  V at 20 K.

Figure 4(c) shows the simulated  $I_{\rm ds}-V_{\rm ds}$  characteristics for the MTJ with  $C_{\rm g}$  present at varying numbers of islands. Removing  $C_{\rm g}$  at the first island increases  $V_{\rm t}$  compared to an MTJ with all  $C_{\rm g}$  present, from  $V_{\rm t}=0.3$  to 0.7 V. As  $C_{\rm g}$  is removed from increasing numbers of islands,  $V_{\rm t}$  increases further, until  $V_{\rm t}>3$  V for all  $C_{\rm g}$  removed. This is due to the reduction in array capacitance looking from the first island into the array, leading to smaller voltage drops across the first tunnel junction and an increase in  $V_{\rm t}$ . Furthermore, as

Fig. 4. (Color online) Single electron Monte Carlo simulations for an MTJ with N=8. Curves offset from each other by 0.05 nA for clarity for (a)–(c). (a) Coulomb staircase  $I_{ds}$ – $V_{ds}$  characteristics at 300 K, for single  $C_g$  removed at an island (b) Coulomb staircase  $I_{ds}$ – $V_{ds}$  characteristics from 300–4.2 K, for  $C_g$  removed at the fourth island. (c) Coulomb staircase  $I_{ds}$ – $V_{ds}$  characteristics at 300 K, for  $C_g$  removed at multiple islands. (d) Experimental (circles) and simulated (triangles) data at 300 K for a nanochain SET with eight islands.  $I_{ds}$  is plotted using a log (main figure) and linear (inset) scale.

we remove  $C_{\rm g}$  from increasing numbers of islands, the steps in the Coulomb staircase become harder to observe.

In some of our devices, the effect of the bottleneck is very strong. Figure 4(d) shows experimental and simulation data from an eight junction MTJ, where the experimental data is from our earlier work. Here,  $I_{ds}$  is plotted on log (main figure) and linear (inset) scales. The very strong second step at  $\sim$ 1.5 V can now be explained by a conduction bottleneck. Removing  $C_g$  at the fourth island and using  $C = 0.12 \,\mathrm{aF}$  and  $C_{\mathrm{g}} = 0.12 \,\mathrm{aF}$ , the simulation predicts the low value of  $V_t = 0.45 \,\mathrm{V}$ , a large current step at 1.5 V, and tends to give a rapid rise in current above  $\sim 3 \text{ V}$ , similar to the experimental data. Here,  $C_{\rm eff} = 0.27\,{\rm aF}$ , the average tunnel junction resistance  $R_{\rm av} = 6\,\rm G\Omega$ , and there is a random variation in  $R_n$  within 60% of  $R_{av}$  (maximum value:  $9.4\,\mathrm{G}\Omega$ , minimum value:  $2.8\,\mathrm{G}\Omega$ ). Here, the corresponding value of  $E_c$  for a SiNC within the array is  $E_c =$  $e^2/2C_{\rm eff} \sim 0.3 \, {\rm eV}, \sim 11 k_{\rm B}T$  at 300 K. For the fourth island,  $C_{{\rm eff},k} \approx 2C_{\rm h} = 0.15\,{\rm aF}$ , a reduction compared to  $C_{{\rm eff}} =$ 0.27 aF. This increases  $E_{\text{c},k} = e^2/2C_{\text{eff},k} = 0.53 \text{ eV} \sim$  $20k_{\rm B}T$  at 300 K. Furthermore, as the removal of  $C_{\rm g}$  from multiple islands simultaneously weakens the steps in the Coulomb staircase [Fig. 4(c)], the presence of strong steps in our data suggests only one, or at most a few islands, have reduced capacitance.

#### 4. Conclusions

We have studied electrical characteristics of SETs fabricated using single Si nanochains at 300 K. Strong Coulomb staircases with varying current step height were observed in the  $I_{ds}$ - $V_{ds}$  characteristics, and single-electron oscillations were observed in the  $I_{\rm ds}$ - $V_{\rm gs}$  characteristics. Monte Carlo simulations were used to investigate the characteristics by considering a nanochain as an MTJ, where the gate capacitance  $C_g$  at the islands is significant compared to the tunnel junction capacitance C. Here, the effective capacitance  $C_{\rm eff}$  for islands within the MTJ is reduced due to the presence of the capacitive array on either side, strengthening the Coulomb staircase at 300 K.  $C_{\rm eff} \sim 0.27\,{\rm aF}$  for the experimental data in Fig. 4(d), giving a large value of  $E_{\rm c} = e^2/2C_{\rm eff} \sim 0.3 \,{\rm eV} \sim 11k_{\rm B}T$  at 300 K. From 300–20 K, the Coulomb staircase shows a large increase in the Coulomb blockade width, much greater than can be explained by a reduction in the thermally activated current at the Coulomb blockade edge. Furthermore, in some devices, a given current step can be larger than others,

improving the clarity of the Coulomb staircase at room temperature. We find that the essential features in our data may be explained by inhomogeneity in the MTJ, associated with a reduced total capacitance at an island well within the MTJ. The higher charging energy associated with such an island leads to a "bottleneck" in conduction, suppressing current at lower voltages and leading to a large current step in the Coulomb staircase. The single-electron charging energy at such an island can be very high,  $\sim 20k_{\rm B}T$  at 300 K.

# **Acknowledgements**

The work was supported by Grants-in-Aid for Scientific Research (Nos. 22246040 and 19-07107) from the Japan Society for the Promotion of Science (JSPS). MAR would like acknowledge the support from JSPS.

- H. Grabert and M. H. Devoret: Single Charge Tunneling Coulomb Blockade Phenomena in Nanostructures (Plenum Press, New York, 1991) NATO ASI Series B.

- A. T. Tilke, F. C. Simmel, R. H. Blick, H. Lorenz, and J. P. Kotthaus: Prog. Quantum Electron. 25 (2001) 97.

- 3) K. K. Likharev: Proc. IEEE 87 (1999) 606.

- 4) K. K. Likharev: IEEE Trans. Magn. 23 (1987) 1142.

- H. Ishikuro, T. Fujii, T. Saraya, G. Hashiguchi, T. Hiramoto, and T. Ikoma: Appl. Phys. Lett. 68 (1996) 3585.

- K. Yano, T. Ishii, T. Hashimoto, T. Kobayashi, F. Murai, and K. Seki: IEEE Trans. Electron Devices 41 (1994) 1628.

- A. Tilke, R. H. Blick, H. Lorenz, and J. P. Kotthaus: J. Appl. Phys. 89 (2001) 8159.

- M. Saitoh, N. Takahashi, H. Ishikuro, and T. Hiramoto: Jpn. J. Appl. Phys. 40 (2001) 2010.

- 9) M. Saitoh, H. Majima, and T. Hiramoto: Jpn. J. Appl. Phys. **42** (2003)

- H. Inokawa, A. Fujiwara, and Y. Takahashi: Jpn. J. Appl. Phys. 41 (2002)

- A. Tilke, R. H. Blick, H. Lorenz, J. P. Kotthaus, and D. A. Wharam: Appl. Phys. Lett. 75 (1999) 3704.

- N. Takahashi, H. Ishikuro, and T. Hiramoto: Appl. Phys. Lett. 76 (2000) 209.

- 13) A. Fujiwara and Y. Takahashi: Nature 410 (2001) 560.

- 14) Y. Takahashi, T. Ishiyama, and M. Tabe: Appl. Phys. Lett. 65 (1994) 2987.

- 15) U. Meirav and E. B. Foxman: Semicond. Sci. Technol. 11 (1996) 255.

- Y. Takahashi, Y. Ono, A. Fujiwara, and H. Inokawa: J. Phys.: Condens. Matter 14 (2002) R995.

- K. Yano, T. Ishii, T. Sano, T. Mine, F. Murai, T. Hashimoto, T. Kobayashi,

T. Kure, and K. Seki: Proc. IEEE 87 (1999) 633.

- S. Kano, Y. Azuma, M. Kanehara, T. Teranishi, and Y. Majima: Appl. Phys. Express 3 (2010) 105003.

- H. Miyazaki, S. Odaka, T. Sato, S. Tanaka, H. Goto, A. Kanda, K. Tsukagoshi, Y. Ootuka, and Y. Aoyagi: Appl. Phys. Express 1 (2008) 024001.

- Y. Takahashi, M. Nagase, H. Namatsu, K. Kurihara, K. Iwadate, Y. Nakajima, S. Horiguchi, K. Murase, and M. Tabe: Electron. Lett. 31 (1995) 136.

- T. Kitade, K. Ohkura, and A. Nakajima: Appl. Phys. Lett. 86 (2005) 123118.

- 22) H. Ishikuro and T. Hiramoto: Appl. Phys. Lett. 71 (1997) 3691.

- M. Saitoh, T. Saito, T. Inukai, and T. Hiramoto: Appl. Phys. Lett. 79 (2001) 2025.

- 24) K. Uchida, J. Koga, R. Ohba, and A. Toriumi: IEEE Trans. Electron Devices 50 (2003) 1623.

- 25) M. Saitoh and T. Hiramoto: Appl. Phys. Lett. 84 (2004) 3172.

- Y. T. Tan, T. Kamiya, Z. A. K. Durrani, and H. Ahmed: J. Appl. Phys. 94 (2003) 633.

- 27) M. A. Rafiq, Z. A. K. Durrani, H. Mizuta, A. Colli, P. Servati, A. C. Ferrari, W. I. Milne, and S. Oda: J. Appl. Phys. 103 (2008) 053705.

- 28) A. Colli, A. Fasoli, P. Beecher, P. Servati, S. Pisana, Y. Fu, A. J. Flewitt, W. I. Milne, J. Robertson, C. Ducati, S. De Franceschi, S. Hofmann, and A. C. Ferrari: J. Appl. Phys. 102 (2007) 034302.

- H. Y. Peng, N. W. Wang, W. S. Shi, Y. F. Zhang, C. S. Lee, and S. T. Lee: J. Appl. Phys. 89 (2001) 727.

- 30) H. Kohno, S. Takeda, and T. Akita: Appl. Phys. Lett. 89 (2006) 233124.

- 31) H. Kohno and S. Takeda: Nanotechnology 18 (2007) 395706.

- T. Nogami, Y. Ohno, S. Ichikawa, and H. Kohno: Nanotechnology 20 (2009) 335602.

- 33) Z. Z. Sun, X. R. Wang, R. Q. Zhang, and S. T. Lee: J. Appl. Phys. 103 (2008) 103719.

- 34) K. Ohkura, T. Kitade, and A. Nakajima: J. Appl. Phys. 98 (2005) 124503.

- 35) We use the single-electron circuit simulator "SIMON", see C. Wasshuber, H. Kosina, and S. Selberherr: IEEE Trans. Comput.-Aided Des. 16 (1997) 937.