# Integration of Self-Assembled Inductors with CMOS LC Oscillators

A.G. Mukherjee<sup>#1</sup>, S. Vatti<sup>#2</sup>, M. E. Kiziroglou<sup>#3</sup>, R. W. Moseley\*<sup>4</sup>, C. Papavassiliou<sup>#5</sup>, A. S. Holmes\*<sup>#6</sup> and E. M. Yeatman\*<sup>#7</sup>

\*Department of Electrical and Electronic Engineering, Imperial College London, SW7 2AZ, U.K.

$^{1}a.mukherjee@imperial.ac.uk, \ ^{2}sofia.vatti04@imperial.ac.uk, \ ^{3}\ m.kiziroglou@imperial.ac.uk \ c.papavas@imperial.ac.uk, \ ^{6}a.holmes@imperial.ac.uk, \ ^{7}e.yeatman@imperial.ac.uk \$

\*Microsaic Systems Ltd, GMS House, Boundary Rd, Woking GU21 5BX, U.K.

4 rmoseley@microsaic.com

Abstract — The quality factor (Q) of integrated inductors is of great importance to radio frequency applications. Monolithic integration of out-of-plane Au inductors with Complementary Metal-Oxide-Semiconductor (CMOS) LC oscillators is reported in this paper. The recently developed self-assembly process involves in-plane fabrication of Au inductors and subsequent rotation of the structure by surface tension forces of a melting Sn hinge. The CMOS compatibility of this process is demonstrated through the integration of an LC oscillator with the self-assembled inductor using post-CMOS processing. At a 1.48 GHz oscillation frequency, a phase noise of -95 dBc/Hz is reported at a 100 kHz frequency offset. Obtained results show this technique to be promising for the integration of high Q inductors with commercial RF systems.

Index Terms — MEMS, RF oscillators, integrated inductors.

# I. INTRODUCTION

Inductors are essential components for radio frequency (RF) circuits. Numerous on-chip Q-improvement techniques have been developed, including micro-machining technologies developed to build RF micro-electro-mechanical systems (RF MEMS). Micro-machining techniques traditionally used to improve inductor Q involve [1], [2]:

- (i) Thick metal electroplating to reduce the inductor series resistance (this is primarily used at 0.2 6 GHz);

- (ii) Implementing 3D solenoid-type inductors to result in large-value designs suitable for 0.2 6 GHz;

- (iii) Substrate etching underneath the inductor to reduce the parasitic capacitance to the substrate (suitable for 1-100 GHz);

- (iv) Rotation of the inductor away from the substrate to reduce the parasitic coupling to the latter (suitable for 1-100 GHz).

In this paper we focus on the integration above CMOS of the self-assembled vertical inductor introduced in [3]. This involves in-plane inductor fabrication and subsequent rotation, using the surface tension forces of a melting hinge. Commercial exploitation of this technique has been limited by the lack of passivation capability required to prevent oxidation of Cu

The phase noise at a given offset of an LC oscillator is proportional to the  $1/Q^2$  of the inductor employed. LC oscillators can therefore be used to directly evaluate the benefits of employing a MEMS inductor. Examples of MEMS inductors

integrated with CMOS oscillators have been previously demonstrated by [5-8].

In this paper we present the integration of the self-assembled inductor proposed in [3, 4] with a complementary cross-coupled LC oscillator implemented in 0.18 um CMOS technology. We describe the fabrication process adopted for the inductor integration, as well as the design and layout of the LC oscillator. Final measurements are presented and compared to published results for LC oscillators with integrated MEMS inductors.

### II. DESIGN AND FABRICATION

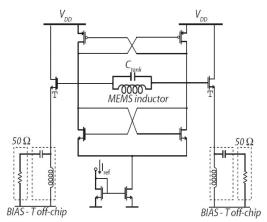

For ease of comparison with previous work, the use of sophisticated designs was avoided, both for the oscillator and the inductor architecture. Thus, a complementary cross-coupled LC oscillator was designed, as shown in Fig. 1, and an RF MEMS meander geometry was adopted for the inductors.

The integration of the MEMS inductor has been performed on 5 mm X 5 mm dies fabricated as part of a Multi-Project-Wafer run in the UMC 0.18 um CMOS technology (6 metal layers, 1 poly layer).

Fig. 1. Schematic of the complementary cross-coupled LC oscillator designed for integration with the MEMS inductor.

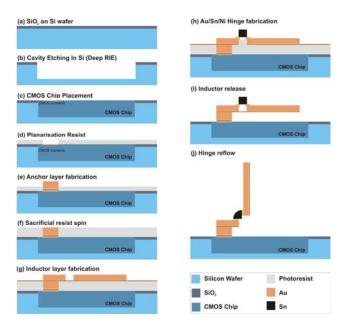

Fig. 2. Post-CMOS MEMS process flow using a carrier wafer.

The fabrication process for the MEMS inductors is summarized in Fig. 2. A carrier wafer is used, allowing postprocessing of individual multi project wafer dies [9]. Commensurate cavities are etched by deep RIE (reactive ion etching) in an oxidized Si wafer to accommodate the dies. These are affixed into the cavities by a planarization photoresist layer. Au anchors are fabricated onto associated CMOS contacts by seed layer sputtering, photoresist patterning electrodeposition of a 3.3 um thick Au layer. A sacrificial resist layer is then spun and patterned to allow the release of the coil structure from the substrate. Subsequently, the Au coil layer and a Sn hinge structure are fabricated with thicknesses 5.3 um and 10 um respectively. The sacrificial resist is stripped, releasing the Au coils and finally, the coil is rotated to the desired angle by reflowing the Sn hinge.

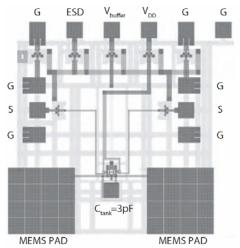

The layout of the oscillator designed for the MEMS inductor integration is shown in Fig. 3. Multiple oscillator structures were implemented on a single die and effort was put into achieving a common pad geometry in order to ease measurements. Probing was chosen as opposed to packaging in order to minimise capacitive loading of the high frequency oscillation signal.

The size of the pads used for dc and RF signals is 59 um x 59 um. The oscillator supply and output Ground-Signal-Ground (GSG) pads form a pi-like structure. Supply pads include dc current/voltage sources, ground and dc control signals. A separate dc pad is always dedicated to the supply of the ESD (electrostatic discharge) protection circuit, to be powered up prior to all other circuit supplies. The GSG output signal pads

Fig. 3. Layout of oscillator to integrate RF MEMS inductor.

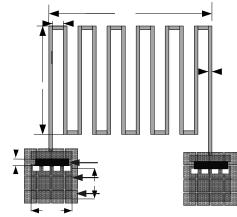

Fig. 4. MEMS meander inductor layout with pad 150 um X 200 um and track of 15 um on CMOS 4 X 4 arrays of pads.

are placed symmetrically at the sides of each oscillator, with a pitch of 100 um.

Finally, a 4 X 4 array of pads provides a large conductive area to electrically connect the MEMS inductor pads and the oscillator circuit. The layout of the MEMS inductor is shown in Fig. 4, where the pads, hinge and meander are shown with their dimensions. The inductor occupies a total area of 770 um X 800 um when in-plane.

## III. MEASUREMENTS

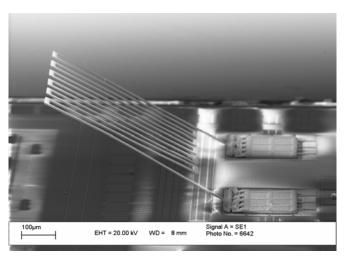

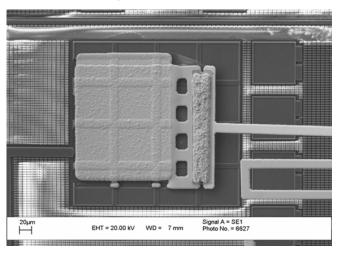

An SEM image of an integrated inductor self-assembled at 30° is shown in Fig. 5. The coil has rotated with respect to the CMOS die resulting in a large coil-circuit distance. This is beneficial to the Q of the inductor as it reduces parasitic effects through the conducting CMOS layers. The junctions between the inductor and the circuit can also be observed. A closer, topview SEM image of the conducting MEMS – CMOS interface is shown in Fig. 6. The 4 X 4 array of CMOS pads allows easy

Fig. 5. SEM image of a MEMS inductor self-assembled at 30° on a CMOS chip.

Fig. 6: SEM image of the electrical MEMS pad on CMOS 4x4 array of pads.

alignment and good conductivity. Contacts for dc probing are also visible on the right of the image, below the inductor track. The Au MEMS pad has been electrodeposited on top of the CMOS contact array. The array texture has propagated during electrodeposition to the surface of the pad.

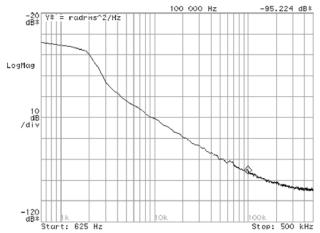

The oscillator circuit in Fig. 1, with the integrated MEMS inductor rotated at a 30° angle, was measured. An oscillation frequency of 1.48 GHz was obtained. The measured phase noise is plotted in Fig. 7. A value of -95 dBc/Hz was achieved at a 100 kHz offset for a -17 dBm output signal power. The oscillator draws a total of 6 mA from a 1.8 V supply. The oscillator measured results also demonstrate the CMOS compatibility of the proposed monolithic integration method.

## III. DISCUSSION

To compare the overall oscillator performance to that of other works reported in the literature, knowledge of the inductor quality factor is required.

Fig. 7. Measured phase noise performance for an oscillator integrated with a MEMS inductor.

For this reason, the equivalent MEMS inductors fabricated on a  $SiO_2/Si$  substrate were characterised. A Q of 5 was observed around the 1.4 GHz oscillation frequency. The maximum Q was 10 at 5 GHz. Pad de-embedding analysis results in doubling of Q, revealing that the performance is limited by the pads' capacitance to the substrate. Since the same MEMS pads have been used for the integrated inductors, similar pad effects are expected for the inductor performance in the oscillators. Therefore, a value of Q = 5 is assumed.

To assess the performance of the oscillator the following figure of merit  $FOM_{ode}$  is employed [10], where *ode* stands for oscillator design efficiency.

$$FOM_{ode} = -10\log\left(\mathcal{L}(f_m)\right) + 10\log\left(\frac{kT}{2P_{DC}} \cdot \frac{1}{Q_u^2} \cdot \frac{f_{osc}^2}{f_m^2}\right)$$

$P_{DC}$  denotes the power consumption of the oscillator.  $Q_u$  is the quality factor of the tank which in our case is approximately equal to that of the inductor. Finally,  $\mathcal{L}(f_m)$  is the phase noise level evaluated at an offset frequency  $f_m$  away from the oscillation frequency  $f_{osc}$ .

FOM<sub>ode</sub> is an absolute benchmark and assesses the feasibility of achieving a certain  $\mathcal{L}(f_m)$  specification for a given power budget and technology (inductor Q factor). This entails comparing the achieved  $\mathcal{L}(f_m)$  with an estimation of the minimum  $\mathcal{L}(f_m)$  that could be achieved from a specific design.

Since  $FOM_{ode}$  measures efficiency, its value can range from 0 to 100 %, or alternatively from  $-\infty$  to 0 dB. State of the art

TABLE I

PERFORMANCE SUMMARY OF PUBLISHED OSCILLATORS WITH MEMS INTEGRATED INDUCTORS

| Ref.      | Turns | P <sub>DC</sub> <sup>a</sup><br>[mW] | f <sub>osc</sub><br>[GHz] | L<br>[nH]          | $Q_{L}$ | $\mathcal{L}\left(f_{m}\right)$ [dBc/Hz] | f <sub>m</sub><br>[kHz] | P <sub>s,50</sub> [dBm] <sup>b</sup> | FOM <sub>ode</sub> |

|-----------|-------|--------------------------------------|---------------------------|--------------------|---------|------------------------------------------|-------------------------|--------------------------------------|--------------------|

| This work | 6     | 10.8                                 | 1.48                      | 3.5-4 <sup>c</sup> | 5°      | -115                                     | 1000                    | -17                                  | -22.8              |

| [5]       | 2.5   | 6.3                                  | 2.8                       | 1.53               | 18.2    | -121                                     | 600                     | NA                                   | -19.5              |

| [6]       | 2.5   | 3.75                                 | 5                         | 1                  | 30      | -122                                     | 1000                    | 0                                    | -16.2              |

| [7]       | 3.5   | 15                                   | 1                         | 5                  | 20      | -124                                     | 300                     | 0                                    | -20.2              |

| [8]       | 6     | 10-13                                | 1.2                       | 4                  | 40      | -110.9                                   | 100                     | -1.5                                 | -27.6              |

<sup>&</sup>lt;sup>a</sup> Power consumption of the oscillator core only.

oscillators reported in the literature range between 10% and 20% in design efficiency [10], i.e. have a  $FOM_{ode}$  between -10 dB and -20 dB.

Table 1 [11] reports recent published CMOS oscillators with integrated MEMS inductors, including the work presented. This is the first vertical self-assembled inductor reported in the literature to be integrated over a CMOS LC oscillator. Prior to this work, a self-assembled inductor (solenoid type) has been reported as used in the design of an LC oscillator in a bipolar process [8].

Since the phase noise level at the output of an oscillator is directly proportional to the output signal power, precise evaluation of  $FOM_{ode}$  should include the power consumption not only of the core of the oscillator, but of any output/amplifying stages leading to the reported output signal power. However, it is customary to account only for the oscillator core consumption when reporting the  $P_{DC}$  value.

Although this work appears to have lower  $FOM_{ode}$ , it should be considered that the output signal power for the design presented is  $\approx \! 17$  dBm lower than the average reported in published designs. Including an amplifying output stage in the circuit design would increase the output signal power and lead to a higher  $FOM_{ode}$  value.

# IV. CONCLUSION

Successful fabrication and integration of the self-assembled inductor onto an LC oscillator circuit in a commercial CMOS technology was demonstrated. The self-assembly process developed for out-of-plane inductor fabrication has been shown to be CMOS compatible. A 1.48 GHz LC oscillator was designed and a phase noise of -95 dBc/Hz at 100 kHz offset was achieved. Measurements obtained from the integration of the CMOS LC oscillator with the proposed MEMS inductor suggest this to be a promising technique for achieving high performance, commercially viable RF integrated circuits.

### ACKNOWLEDGEMENT

This work was supported by the EPSRC. The authors would like to thank Stepan Lucyszyn for useful discussions.

### REFERENCES

- [1] G. M. Rebeiz, RF MEMS: Theory, Design, and Technology, Wiley-Interscience, Mar. 2003.

- [2] S. Lucyszyn, "Review of radio frequency microelectromechanical systems technology," *Proceedings of IEE Science, Measurement and Technology*, vol. 151, no. 2, pp. 93-103, Mar. 2004.

- [3] G. W. Dahlmann, E. M. Yeatman, P. Young, I. D. Robertson, and S. Lucyszyn, "Fabrication, RF characteristics and mechanical stability of self-assembled 3D microwave inductors," *Sensors and Actuators A: Physical*, vol. 97-98, pp. 215-220, 2002.

- [4] M. E. Kiziroglou, A. G. Mukherjee, R. W. Moseley, P. Taylor, S. Pranonsatit, A. S. Holmes, and E. M. Yeatman, "Electrodeposition of Au for Self-Assembling 3D Micro-Structures," presented at SPIE Micromachining and Microfabrication Process Technology XIII, San Jose, U.S.A., 2008.

- [5] H.-C. Chen, C.-H. Chien, H.-W. Chiu, S.-S. Lu, K.-N. Chang, K.-Y. Chen, S.-H. Chen, "A low-power low-phase-noise LC VCO with MEMS Cu inductors," *IEEE Microwaveand Wireless Components Letters*, vol. 15, no. 6, pp. 434-436, June 2005.

- [6] E.C. Park, S.H. Baek, T.S. Song, J.B. Yoon, E. Yoon, "Performance comparison of 5GHz VCOs integrated by CMOS compatible high Q MEMS inductors," *IEEE International Microwave Symposium Digest*, vol. 2, pp. 721-724, June 2003.

- [7] E.-C. Park, Y.-S. Choi, J.-B. Yoon, S. Hong, E. Yoon, "Fully integrated low phase-noise VCOs with on-chip MEMS inductors," *IEEE Transactions on Microwave Theory and Techniques*, vol. 51, no. 1, pp. 289-296. Jan. 2003.

- [8] K. Van Schuylenbergh, C.L. Chua, D.K. Fork, J.P. Lu, B. Griffiths, "On-chip out-of-plane high-Q inductors," *Proceedings of IEEE Lester Eastman Conference on High Performance Devices*, pp. 364-373, Aug. 2002.

- [9] A. G. Mukherjee, M. E. Kiziroglou, A. S. Holmes, and E. M. Yeatman, "MEMS Post-Processing of MPW Dies using BSOI Carrier Wafers," presented at SPIE Micromachining and Microfabrication Process Technology XIII, San Jose, U.S.A., 2008.

- [10] J. van der Tang, D. Kasperkovitz, "Oscillator design efficiency: a new figure of merit for oscillator benchmarking," *Proceedings of IEEE International Symposium on Circuits and Systems*, vol. 2, pp. 533-536, May 2000.

- [11] S. Vatti, RF CMOS VCOs: MEMS Inductor Integration and the Bias-Tuning Method, PhD thesis, Imperial College London, pp. 114, Aug. 2008.

<sup>&</sup>lt;sup>b</sup> Output signal power on a 50Ω load.

<sup>&</sup>lt;sup>c</sup> Values for a MEMS inductor developed over a passive silicon substrate with thick oxide layers.