## Imperial College of Science, Technology and Medicine

DEPARTMENT OF COMPUTING

BENG MATHEMATICS AND COMPUTER SCIENCE INDIVIDUAL PROJECT

# Optimising finite-difference methods for PDEs through parameterised time-tiling in Devito

Nicholas SIM

Supervisors Prof. Paul H. J. KELLY Dr Fabio LUPORINI SUN Tianjiao

Second marker Dr Gerard GORMAN

June 2018

#### Abstract

Finite-difference methods are widely used in solving partial differential equations. In a large problem set, approximations can take days or weeks to evaluate, yet the bulk of computation may occur within a single loop nest. The modelling process for researchers is not straightforward either, requiring models with differential equations to be translated into stencil kernels, then optimised separately. One tool that seeks to speed up and eliminate mistakes from this tedious procedure is Devito, used to efficiently employ finite-difference methods.

In this work, we implement *time-tiling*, a loop nest optimisation, in Devito yielding a decrease in runtime of up to 45%, and at least 20% across stencils from the acoustic wave equation family, widely used in Devito's target domain of seismic imaging. We present an estimator for *arithmetic intensity under time-tiling* and a model to predict runtime improvements in stencil computations. We also consider generalisation of time-tiling to imperfect loop nests, a less widely studied problem.

#### Acknowledgements

To my supervisors, Prof. Paul Kelly and Dr. Fabio Luporini, my deepest thanks are due for their invaluable advice and insight, for the clearest explanations which I can only hope to emulate, and for igniting my interest in computer architecture. I must also thank Sun Tianjiao, who provided much-needed early guidance on performance testing and regular advice throughout. These people made this project a delight to work on.

Thanks also to my parents, for their boundless support. To them I owe this and my sense of determination. Finally, my unqualified gratitude goes to friends who remind me of the greater context of this—and every—work.

# Contents

| Abstract 3         |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Acknowledgements 5 |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Intr               | oductic                                                                                     | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 1.1                | Motiv                                                                                       | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 1.2                | Contri                                                                                      | ibutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 1.3                | Repor                                                                                       | t structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Bacl               | kgroun                                                                                      | d and related work                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 2.1                | Termi                                                                                       | nology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 2.2                | Loop                                                                                        | tiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.2.1                                                                                       | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.2.2                                                                                       | Insight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.2.3                                                                                       | Strip-mining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.2.4                                                                                       | Loop interchange                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 2.3                | Tiling                                                                                      | in the time dimension                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.3.1                                                                                       | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.3.2                                                                                       | Skewing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 2.4                | Devito                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.4.1                                                                                       | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.4.2                                                                                       | Domain-specificity                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.4.3                                                                                       | Layers of abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.4.4                                                                                       | Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 2.5                | Surve                                                                                       | y of related work                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.5.1                                                                                       | Halide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.5.2                                                                                       | Pochoir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.5.3                                                                                       | YASK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.5.4                                                                                       | OPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | 2.5.5                                                                                       | Firedrake                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 2.6                | 2.6 Summary                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                    | <pre>cknov<br/>Intro<br/>1.1<br/>1.2<br/>1.3<br/>Bacl<br/>2.1<br/>2.2<br/>2.3<br/>2.4</pre> | cknowledged         Introduction         1.1       Motiv         1.2       Contri         1.3       Repor         Backgroun         2.1       Termin         2.2       Loop f         2.1       Z.2.1         2.2       Z.2.3         2.2.4       Z.3.1         2.3       Tiling         2.3.1       Z.3.2         2.4       Devito         2.4.1       Z.4.2         2.4.3       Z.4.4         2.5       Survey         2.5.1       Z.5.2         2.5.3       Z.5.4         2.5.5       Z.5.5 | Eknowledgements         Introduction         1.1       Motivation         1.2       Contributions         1.3       Report structure         Background and related work         2.1       Terminology         2.2       Loop tiling         2.2.1       Motivation         2.2.2       Insight         2.2.3       Strip-mining         2.2.4       Loop interchange         2.3       Tiling in the time dimension         2.3.1       Motivation         2.3.2       Skewing         2.4       Deop interchange         2.4       Domain-specificity         2.4.2       Domain-specificity         2.4.3       Layers of abstraction         2.4.4       Architecture         2.5       Survey of related work         2.5.1       Halide         2.5.2       Pochoir         2.5.3       YASK         2.5.5       Firedrake |  |  |  |

| 3 | Space-tiling and the Devito compilation process |         |                                                   |    |

|---|-------------------------------------------------|---------|---------------------------------------------------|----|

|   | 3.1                                             | Overv   | 7iew                                              | 29 |

|   | 3.2                                             | The D   | Pevito symbolic engine (DSE)                      | 30 |

|   |                                                 | 3.2.1   | Common sub-expression elimination (CSE)           | 30 |

|   |                                                 | 3.2.2   | Indexing                                          | 31 |

|   | 3.3                                             | The D   | Pevito loop engine (DLE)                          | 31 |

|   |                                                 | 3.3.1   | Loop fission                                      | 31 |

|   |                                                 | 3.3.2   | OpenMP pragmas and parallelisation                | 32 |

|   | 3.4                                             | Spatia  | I tiling in Devito                                | 32 |

|   |                                                 | 3.4.1   | Parameterisation                                  | 32 |

|   |                                                 | 3.4.2   | Auto-tuner                                        | 32 |

|   |                                                 | 3.4.3   | Determination of tile sizes                       | 33 |

|   |                                                 | 3.4.4   | Remainder loops                                   | 33 |

|   | 3.5                                             | Summ    | nary                                              | 33 |

| _ | _                                               |         |                                                   |    |

| 4 | -                                               | lement  |                                                   | 35 |

|   | 4.1                                             |         | ing                                               |    |

|   |                                                 | 4.1.1   | Common sub-expression elimination                 |    |

|   |                                                 | 4.1.2   | Implementation                                    |    |

|   | 4.2                                             |         | tiling                                            |    |

|   |                                                 | 4.2.1   | Aligning the loop bounds                          |    |

|   |                                                 | 4.2.2   | Min/max bounds for valid array accesses           | 37 |

|   |                                                 | 4.2.3   | Parallelisation of loops                          | 39 |

|   |                                                 | 4.2.4   | Implementation                                    |    |

|   | 4.3                                             |         | uite                                              |    |

|   | 4.4                                             |         | tuning                                            |    |

|   | 4.5                                             |         | nary and further implementation work              |    |

|   |                                                 |         | Source and receiver loops                         | 42 |

|   |                                                 | 4.5.2   | DSE aggressive mode                               |    |

|   |                                                 | 4.5.3   | Minor extensions                                  | 43 |

| 5 | Eva                                             | luation |                                                   | 45 |

| 0 | 5.1                                             |         |                                                   | 46 |

|   | 5.2                                             |         | s for evaluating time-tiling                      | 46 |

|   | 0.2                                             | 5.2.1   | Time-buffering                                    | 46 |

|   |                                                 | 5.2.2   | Auto-tuner iterations                             | 47 |

|   |                                                 | 5.2.3   | Time-tiling parameters                            | 47 |

|   | 5.3                                             |         | metic intensity under time-tiling                 | 48 |

|   | 2.0                                             | 5.3.1   | Arithmetic intensity estimator in Devito          |    |

|   |                                                 | 5.3.2   | Estimating arithmetic intensity under time-tiling |    |

|   |                                                 | 5.3.3   | Tile boundaries determine cache reuse             | 50 |

|   |      | 5.3.4   | Establishing a tighter bound                         | 51 |

|---|------|---------|------------------------------------------------------|----|

|   |      | 5.3.5   | Generalisation to time-tiling                        | 52 |

|   |      | 5.3.6   | Improving the bounds further                         | 53 |

|   |      | 5.3.7   | Minimising runtime based on tile size choices        | 53 |

|   | 5.4  | Testing | g methodology                                        | 54 |

|   |      | 5.4.1   | Hardware and software environment                    | 54 |

|   |      | 5.4.2   | Use of auto-tuner                                    | 55 |

|   |      | 5.4.3   | Functional correctness                               | 55 |

|   |      | 5.4.4   | Experimentation and reporting of runtimes            | 55 |

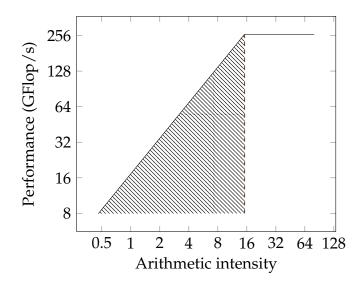

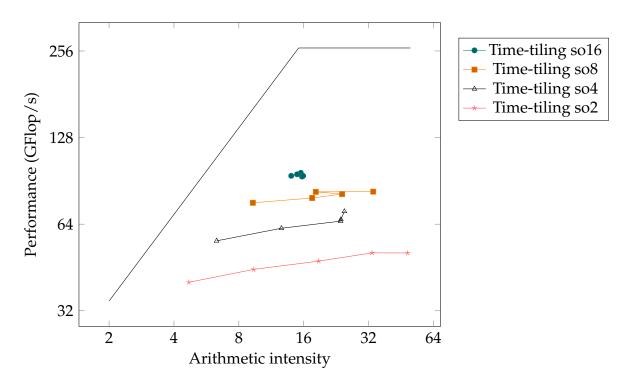

|   | 5.5  | Rooflin | ne model                                             | 56 |

|   |      | 5.5.1   | Bounds of the test machine                           | 56 |

|   |      | 5.5.2   | Arithmetic intensity and cache reuse                 | 56 |

|   | 5.6  | Test pa | arameters                                            | 57 |

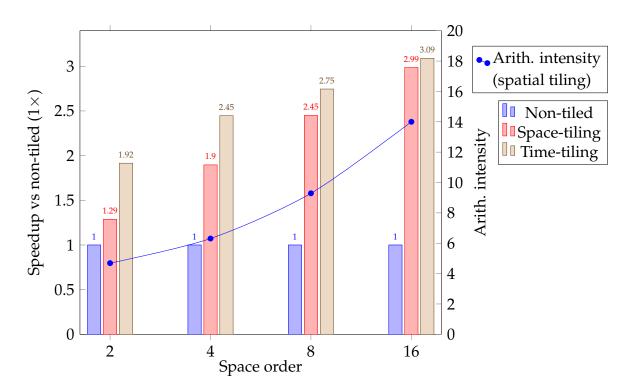

|   | 5.7  | Perfor  | mance of the Laplace operator                        | 58 |

|   |      | 5.7.1   | Application of the operator                          | 58 |

|   |      | 5.7.2   | Results                                              | 58 |

|   | 5.8  | Perfor  | mance of the acoustic wave equation operator         | 62 |

|   |      | 5.8.1   | Application of the operator                          | 62 |

|   |      | 5.8.2   | Results                                              | 62 |

|   | 5.9  | Effect  | of the skewing factor                                | 64 |

|   | 5.10 | Effect  | of the time tile size                                | 66 |

|   | 5.11 | Evalua  | ation of the arithmetic intensity estimator          | 67 |

|   |      | 5.11.1  | Conditions for most accurate estimates               | 67 |

|   |      | 5.11.2  | Modelling performance improvement with the estimator | 67 |

|   |      | 5.11.3  | Comparison to the naive estimator                    | 67 |

|   |      | 5.11.4  | Constructing a better estimator                      | 68 |

|   | 5.12 | Limita  | tions and further evaluation                         | 68 |

|   |      | 5.12.1  | Realism of test problems                             | 68 |

|   |      | 5.12.2  | Test architecture                                    | 69 |

|   |      |         | Memory analyses                                      | 69 |

|   |      | 5.12.4  | Comparison to spatial tiling                         | 69 |

|   |      | 5.12.5  | Time-tiling with larger time dependences             | 70 |

|   |      | 5.12.6  | Further uses for an arithmetic intensity estimator   | 70 |

|   | 5.13 | Summ    | ary                                                  | 71 |

| 6 |      | clusion |                                                      | 72 |

|   | 6.1  |         | xt and review                                        | 72 |

|   | 6.2  |         | butions                                              | 73 |

|   | 6.3  |         | e work                                               | 74 |

|   |      | 6.3.1   | Tiling imperfectly-nested loops                      | 74 |

| 6.3.2        | Advanced manipulation of symbolic expressions                 | 75 |

|--------------|---------------------------------------------------------------|----|

| 6.3.3        | Memory analyses to determine further areas for optimisation   | 76 |

| 6.3.4        | Improvement of the arithmetic intensity estimator bounds, and |    |

|              | uses thereof                                                  | 77 |

| 6.3.5        | Evaluation on more stencils and architectures                 | 77 |

| Bibliography |                                                               | 78 |

# Chapter 1

# Introduction

## 1.1 Motivation

In many engineering domains, finite-difference methods are used to find approximate solutions to differential equations. For scientists using differential equations in novel ways, tools which can transform partial differential equations to optimised computations and evaluate them are useful; this enables them to refine their models quickly.

It is inefficient and undesirable for specialists principally concerned with modelling to optimise their computations by hand. As a means of abstraction, compilers can be used to automatically transform differential equations into stencils, then code to evaluate the equations. A tool automatically performing this transformation saves considerable labour and scope for errors, and reduces the effort required to comprehend the calculations. These aid maintenance and even reproducibility; generating and optimising code by hand is rarely feasible or efficient [24].

Decoupling optimisation from specific models means that domain specialists can take advantage of optimisations seamlessly without intervention, allowing them to focus their attention and expertise on their own domain. They can easily take advantages of the latest advances in computer architecture and new instructions such as vectorisation, which give rise to new optimisations in finite-difference methods.

#### Devito: a tool for solving differential equations

In modern usage, the partial differential equations are transformed into *stencils*, which define the computation, then code to execute it. One of the challenges faced by domain specialists generating new models is the time necessary to perform this translation. Thus the desire for a compiler to save time and effort arises.

Devito [15], a tool for efficient application of finite-difference methods, is able to generate computations directly from differential equations, achieving a notion of 'vertical integration' within the modelling ecosystem. There are several compilers, a number of which we review in Chapter 2, which perform optimisation on stencil kernels, but none which also transform differential equations into stencils. Being able to automate this transformation is extremely helpful if one is experimenting with models, or continually modelling new problems, as one can change the equations used and rapidly generate and execute the relevant computation.

#### Context and existing work in time-tiling

Some stencil compilers are able to apply the *time-tiling* optimisation, which this work implements in Devito. It was previously demonstrated that time-tiling could reduce the run time of 'some Devito stencil loops by up to 27.5%' [21], comparing time-tiling against the existing spatial tiling which the tool is able to perform. In this case another tool, CLooG [5], was used to add time-tiling to Devito-generated code.

While the literature surrounding the polyhedral model, from which time-tiling derives, dates from the last century, it was viewed as complicated and time-consuming to use in optimising compilers as recently as 2004 when Bastoul proposed extensions [5] to the original Quilleré et al. algorithm to eliminate redundant (generated) code [27]. Time-tiling has been studied in the form this work considers since Griebl in 2004 [12], using *space-time mapping*, analogous to the skewed tiling which we discuss in this work, but expressed as affine conditions specifying hyperplane partitions of the problem domain.

Time-tiling has since been studied extensively, and long implemented in polyhedral compilers such as PLUTO, providing a strong theoretical foundation. However, until this work, the actual application of the technique beyond theoretical study has been limited to the OPS (Oxford Parallel library for Structured mesh solvers) project [32], who presented their implementation of time-tiling in 2017 [33]. Even so, OPS is a source-to-source compiler, operating from the stencil kernel level down to code generation; Devito includes all these plus layers of abstraction up to the differential equations themselves, making this a unique implementation and study of time-tiling.

#### Objective

Therefore, we extend tiling to the time dimension natively in Devito to realise this performance gain and evaluate its efficacy. This gives the performance gains of time-tiling to Devito without the need to configure another tool to perform further optimisations.

## 1.2 Contributions

The principal objective of this project was to implement tiling over the time dimension in Devito and evaluate its performance against the existing optimisation, that of tiling restricted to the spatial dimensions.

In summary, the contributions of this thesis are:

- A fully-functional implementation of time-tiling for perfect loop nests in Devito, including a simplification of the generated code structure, with accompanying test cases and auto-tuner enhancements. An analysis of its legality and the necessary conditions to guarantee this.

- An evaluation of the correctness and performance of the time-tiling transformation and any actions end-users may need to take to realise performance gains.

- Demonstration of a runtime decrease of up to 45%, and in general more than 20%, compared to Devito's existing optimisations on kernels from real-world applications, including stencils from the family of acoustic wave equation operators, widely used in Devito's target domain, seismic imaging.

- A novel estimator for *arithmetic intensity under time-tiling* that extends the existing estimator for arithmetic intensity under spatial tiling in Devito, and a proof of its consistency with the widely-cited roofline model. An evaluation of the utility of this estimator compared to a generalised version of the existing estimator, and an analysis of the shortcomings of both. A model to predict when performance improvement is minimal or negative, and a demonstration that stencils of the acoustic wave equation family can benefit further from greater cache reuse.

- An analysis on how parameters introduced by time-tiling, the time tile size and skewing factor, affect the runtime of stencil computations, and the circumstances under which the runtime decrease is maximal.

- A discussion on further implementation work, analysing their importance and consistency with the transformation we have implemented.

## **1.3 Report structure**

This report is divided into 6 chapters, describing the above contributions and the context from which they arise:

- **Chapter 2** A review of the fundamentals needed for time-tiling in general, including its motivation and consequences. A survey of work related to stencil compilers, approximate solvers of partial differential equations, in particular the abstractions that they make available to the user.

- **Chapter 3** Details of the existing Devito compilation process which will be affected by time-tiling, and its existing implementation of spatial tiling.

- **Chapter 4** The implemented time-tiling transformation. Explanations of the design choices made, and modifications to the auto-tuner to ensure time-tiling is used effectively. Proposals for further implementation work arising from time-tiling.

- **Chapter 5** An analysis of the effectiveness of the implemented transformation. Evidence of large performance improvements, and the conditions under which they are most and least significant. The aforementioned estimator for arithmetic intensity under time-tiling and its evaluation. Finally, areas for improvement in identifying and realising greater decreases in runtime.

- **Chapter 6** The conclusion of the work, and a discussion of future work to be done alongside the streamlining of this optimisation process.

**Time-tiling in Devito** The implemented transformation from this work is currently being integrated into the Devito codebase; based on our evaluation, it is expected to bring significant performance improvement to customer applications.

# Chapter 2

# **Background and related work**

We first provide an overview of loop nest optimisations, techniques, and analyses that we have applied, with specific reference to time-tiling. This forms the basis and context for the entire report, and specifically informs our overview of Devito (Section 2.4) and the survey of related work, which composes the remainder of this chapter (Section 2.5).

This project extends a well-established idea from compiler theory, *tiling*, to another dimension (time) in Devito. When tiling, particular attention need be paid to data dependences, locality, and parallelism of the resultant code. Despite the confluence of factors, tiling is a remarkably simple concept. Nevertheless, it is challenging to implement correctly in sufficient generality for Devito, being largely restricted to research compilers apart from OPS; in particular, we implement *parameterised* time-tiling, which allows tile sizes to be changed at runtime.

## 2.1 Terminology

In addition the terms defined in the sections that follow, we use the following definitions widely in the context of this work:

**Iteration space** The *iteration space* is the discretised problem domain that we iterate over. In general, Devito handles hyperrectangular iteration spaces, but in this work it is sufficient to consider three or fewer spatial dimensions and a time dimension. All remarks in this work can be considered to generalise to higher spatial dimensions unless otherwise stated.

**Stencil** A *stencil* defines a computation on an iteration space. In particular, note that a stencil will define the value of a point in terms of its spatial neighbours in previous time iterations. It may be helpful to recall that we are employing finite-difference methods, and Taylor's theorem in higher dimensions.

**Space order** The *space order of a stencil* defines the precision of the resulting computation. A stencil with higher space order will use data from, hence have a dependence on, more distant spatial neighbours. The *radius* of a stencil refers to the distance of the furthest spatial dependency.

**Arithmetic intensity** The *arithmetic intensity of a stencil* is the number of floating point operations performed per byte of data required, given in floating point operations per byte.

## 2.2 Loop tiling

#### 2.2.1 Motivation

The bulk of computation lies in loops [3]. Finite-difference methods are no exception, and in such computations, nested loops ('loop nests') are frequently encountered. Loop nest optimisations seek to transform a loop, possibly changing its execution order to improve data locality, parallelism, or otherwise avoid unnecessary operations.

#### 2.2.2 Insight

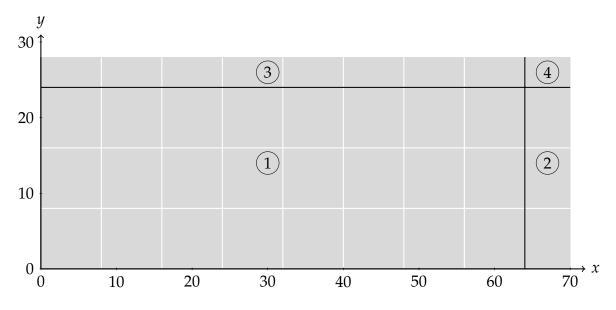

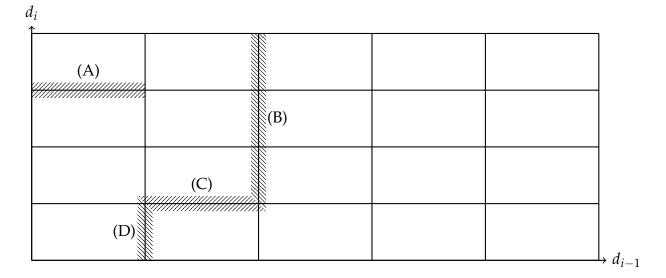

To exploit data locality, we must use data before it gets evicted from the cache; ideally, data is not loaded into the cache more than once. Caching and predicting reuse is a complex process [16]; empirically, reuse does occur within sufficiently small iteration spaces. We therefore contrive small iteration spaces by partitioning the original space into smaller tiles (Figure 2.1).

Loop tiling is also commonly known as *blocking*, or perhaps less transparently *stripmine and interchange*, as tiling is typically achieved through these two transformations.

**Additional motivation** As a remark, the stencils resulting from finite-difference methods tend to have high *arithmetic* intensity, while tiling is used to reduce *memory* pres-

**Figure 2.1:** Tiles over an iteration space. Note that the tile size need not be the same in each dimension, or divide the extent of the iteration cleanly.

sure.<sup>1</sup> However, as we note later, arithmetic intensity can be decreased (at the expense of increasing memory pressure) by eliminating common sub-expressions and other transformations, which would ordinarily result in redundant computation. Further, tiling may also enable other transformations, such as loop-invariant code motion, which again reduces redundant computation.

#### 2.2.3 Strip-mining

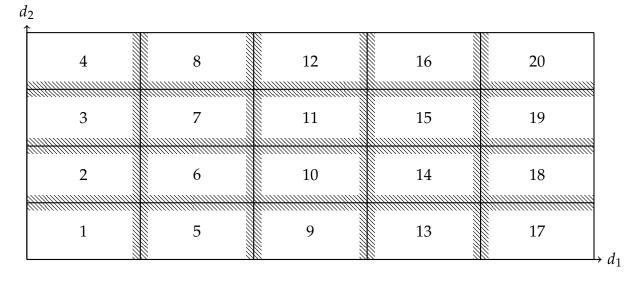

Named after the mining practice, strip-mining involves dividing a dimension of the iteration space into strips (Figure 2.2).<sup>2</sup> By itself, strip-mining does not change the execution order; it is a gateway to further transformations.

Throughout this work, we will refer to the outer loop (variable x\_blk in Figure 2.3) as the *tile* loop, and the inner loop (variable x in the same figure) as the *incremental* loop.

We will need more loops to perform an interchange. Figure 2.3 illustrates a loop that has been strip-mined in two dimensions.

<sup>&</sup>lt;sup>1</sup>Thus stencils may not benefit from memory reuse if the bottleneck occurs at the CPU.

<sup>&</sup>lt;sup>2</sup>However, you cannot divide a dimension into lateral strips, only sequential ones.

```

for (int x = x_start; x < x_end; x++) {

A[x] = B[x-1] + B[x+1];

}

for (int x_blk = x_start ; x_blk < x_end; x_blk += x_blk_size) {

for (int x = x_blk; x < min (x_end, x_blk + x_blk_size); x++) {

A[x] = B[x-1] + B[x+1]; // loop body unchanged

}

}</pre>

```

**Figure 2.2:** A regular loop, and the same loop strip-mined over the variable x. x\_start and x\_end are chosen to prevent out-of-bounds accesses. In case the tile (block) size does not evenly divide the extent of the iteration, the min function avoids the need for remainder loops (discussed in Section 3.4.4). We will abbreviate the variable names in subsequent examples.

**Figure 2.3:** Strip-mining a loop nest iterating over variables x and y. Offsets have been omitted here.

#### 2.2.4 Loop interchange

Loop interchange is based on the observation that a change in execution order does not change the correctness of a strip-mined program. We will change the order of the loops to iterate over the tiles, then within them (Figure 2.4).

This is valid when each point in the iteration space does not depend on the values calculated in the same iteration. Therefore, one must be extremely careful that no data dependences cross boundaries between tiles; if they do, they must be permitted to cross only in one direction, and the tiles must be scheduled in that order. This will become clear in Section 2.3.2.

**Figure 2.4:** The loop nest of Figure 2.3, with the x and y\_blk loops interchanged. This is a *tiled* loop.

## 2.3 Tiling in the time dimension

#### 2.3.1 Motivation

Many problems involving finite difference methods are computationally bounded, rather than bounded by memory throughput. However, it is possible to reduce the operation count by exploiting the structure of expressions computed at the cost of increased memory pressure [18].

We are therefore interested to perform time-tiling in addition to the existing spatial tiling to alleviate the increased memory pressure and realise significant performance gains, possibly 27.5% in Devito alone [21]. This improvement is significant over the optimisation from tiling in all dimensions apart from time [6].

In spatial tiling, we exploited data locality within the computation of a single time iteration. In contrast, time-tiling exploits data locality between time iterations.

#### 2.3.2 Skewing

In Section 2.2.4 we stated that interchange is valid when data dependences do not cross boundaries between tiles. This is clear, as if there are no inter-tile dependences, the tiles can be executed in any order.

A *data dependence* occurs when two statements reference a datum, and at least one statement changes it. Failure to preserve the execution order of the statements is known as *dependency violation*.

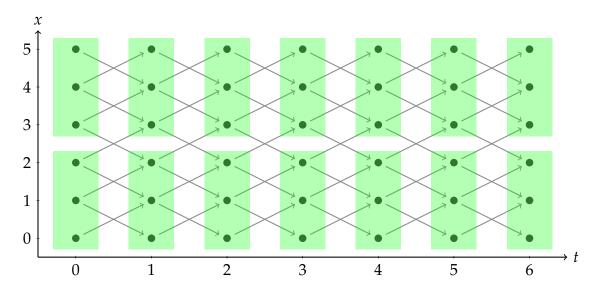

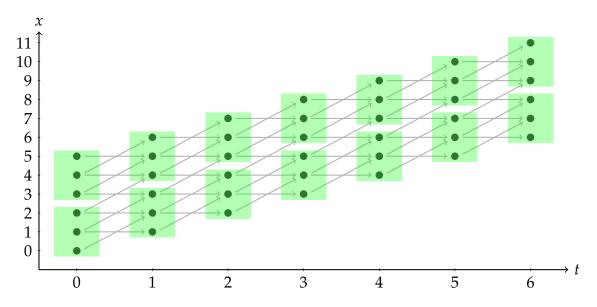

To preserve the dependence, we must preserve the order in which these statements are executed. Figure 2.5 illustrates how dependences may look in a (1-dimensional)

iteration space similar to the problems we discuss later. Dependency violation occurs with an invalid ordering which overwrites data yet to be read, or requires data that has not been calculated yet.

**Figure 2.5:** An iteration space with data dependences indicated by a forward arrow for a value derived from a dependence. It would not be valid to interchange loops over the t and x dimensions here.

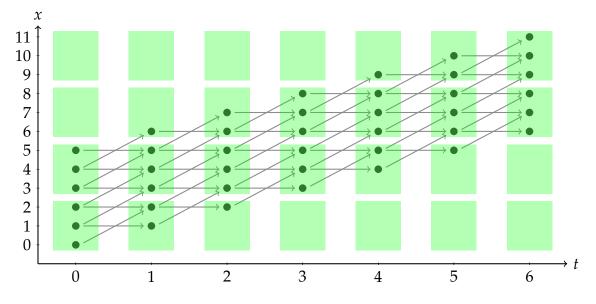

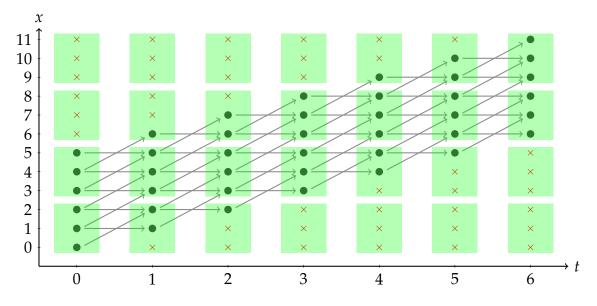

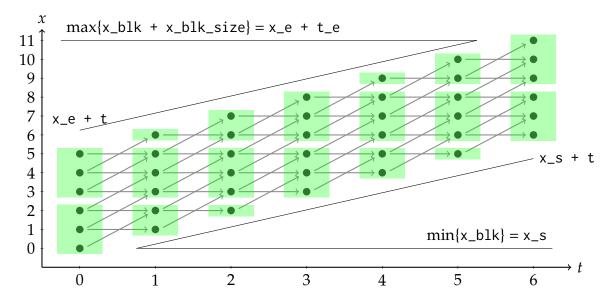

We employ skewing to make the interchange valid (Figure 2.6). This solves the dependency problem [7], and allows for loop interchange.

**Figure 2.6:** The same iteration space skewed by a factor of t in the x dimension. Note that the tiling is now valid (as long as we avoid out-of-bounds accesses) and we can execute the tiles in either dimension first, and that we can merge tiles in the t dimension.

#### Validity of skewing factors

We have seen that skewing is a tool to enable loop interchange, and that interchange is legal when dependences only cross tile boundaries in one direction. To ensure this, a sufficiently large skewing factor must be used. We claim that the maximum spatial dependence distance is a valid skewing factor [38], i.e. in a stencil A[t][x] =c0\*A[t-1][x] + c1\*A[t-1][x-1] + ... + cn\*A[t-1][x-n];, the minimum valid skewing factor is n.

As a remark, in this work we have largely decided to skew all spatial dimensions with this skewing factor, due to its simplicity, and the stencils under consideration. However, it is equally valid to skew each spatial dimension by the dependence distance *for that particular dimension* [34].

#### 2.4 Devito

Devito [15] is a domain-specific language and code generation framework for solving PDEs with finite-difference methods [9]. Its main use case is building solvers for differential equations from high-level mathematical expressions, written using the symbolic library *SymPy*, and is targeted at the domain of seismic imaging.

#### 2.4.1 Motivation

Efficient computation demands that we use every optimisation at our disposal. As computer architecture changes, introducing new instructions, GPUs and distributed systems, specialist research compilers implementing subsets of related optimisations do not suffice for high-performance applications.

An equal part of optimisation is reducing the turnaround time in modelling. Providing an interface that domain specialists are familiar with reduces friction, and removes the need to construct stencils by hand. This also reduces errors by simplifying the inputs that they provide.

This combination of ease of use through the Python and *SymPy* interface and the generation of optimised and fast C code without user intervention make Devito an attractive tool.

#### 2.4.2 Domain-specificity

Polyhedral compilers such as PLUTO [6], with its backend CLooG [5] are able to apply tiling over generic loop nests. Further, the iteration spaces which they handle are

unions of convex polyhedra, again more general than the use cases Devito is likely to encounter. This generality is not necessary when merely applying finite-difference methods to solve differential equations, not least when targeting a specific domain which uses such methods.

We can instead make use of this specificity to make informed choices in our optimisations, or streamline an auto-tuning routine. Further, we are able to combine different optimisations, at the stencil level and progressively lower levels. Finally, considering likely use cases, it may be desirable to target compilation for architectures not supported by more general compilers, such as GPUs.

#### 2.4.3 Layers of abstraction

The separation of symbolic expressions and the underlying C code to which they are compiled is key to Devito's comprehensibility and usage. By progressive manipulation, optimisation and modification is possible at many layers. A further benefit as a more general software engineering practice is the possibility of small unit tests for individual components.

This also allows the integration of other tools, which may fit a user's needs or architectures better, and enables easy benchmarking of Devito's performance against said tools. For instance, YASK (Section 2.5.3) is being integrated as a compilation backend.

An important feature for seismic imaging is sparse-point interpolation. Devito handles this by exposing powerful lower-level APIs to allow the construction of comprehensive representations which would be tedious or impossible at higher levels of abstraction.

#### 2.4.4 Architecture

The Devito compilation process (Chapter 3) can be divided into several stages:

- 1. Construction of stencil equations (symbolic kernel)

- 2. Grouping of expressions

- 3. CSE and indexing of stencil (the Devito symbolic engine (DSE), Section 3.2)

- 4. Loop optimisation and other transformations (the Devito loop engine (DLE), Section 3.3)

- 5. Code generation

Our time-tiling transformation will occur in the DSE and DLE, covered in detail in the respective sections.

## 2.5 Survey of related work

The following sections provide an overview of tools related to Devito and of interest to our investigation. In particular, they identify instances of time-tiling (or equivalent transformations) which have been solved and the insights required, and analyse their applicability to time-tiling in Devito.

#### 2.5.1 Halide

Halide was conceived as a representation for image processing pipelines. Many image processing algorithms are similar to stencils: Halide specifically deals with overlapping stencils; this overlap can be compared to iteration in the time dimension.

#### Insight

It is possible to separate image processing algorithms ("filters") and their schedules [28]. Optimisation for an architecture then becomes an exercise in optimising the schedule and not the filters, which are reduced to kernels.<sup>3</sup> Halide is therefore a stencil compiler.

Modifying schedules is analogous to our loop optimisations: filters can be vectorised, tiled, interchanges are possible, etc. Halide further provides an auto-tuner which estimates, among other things, arithmetic intensity of filters and loop transformations which Devito also employs [29, 23]. Part of its analysis examines the trade-off between additional computation and memory traffic.

#### Applicability

The problem domain, image processing, that Halide is concerned with may appear very different to that of differential equations. However, the underlying natures of the computations are very similar: use of stencil kernels, trade-off between redundant computation and memory pressure, etc. Analogously to time-tiling, Halide is able to compute tiles across filters.

<sup>&</sup>lt;sup>3</sup>See https://github.com/halide/CVPR2015/blob/master/blur.cpp for an example

Likewise, in Devito, *each time iteration* may contain several stencil kernels applied consecutively. To extend the analogy, Halide is concerned with tiling within *a single* timestep, while this project investigates tiling over *multiple* timesteps.

Domain-specific frameworks bring insight to a problem which general-purpose compilers may not possess; the separation of algorithm and schedule, while touted as novel, is essentially what every compiler applies during transformations such as loop interchange.

#### 2.5.2 Pochoir

Pochoir is a compiler for stencil computations focussed on utilising parallelism and multithreading. Stencils are defined with provided C++ templates, from which the computations are generated. Pochoir implements a two-phase compilation strategy: the first involves compilation with the Pochoir template library, which ensures compliance and compatibility with the library. At this stage, one may debug the non-optimised code. The second is the optimisation phase using the Pochoir compiler<sup>4</sup> [35].

#### Insight

**Cache-oblivious algorithms** These seek to eliminate tuning of cuts (tile size) based on cache properties including cache sizes or replacement policies, reasoning that the correct cache-oblivious algorithm will achieve (asymptotically) the same performance [10].

Pochoir uses a cache-oblivious algorithm based on parallel cuts. These *hyperspace* and *time cuts* decompose the iteration spaces ("zoids") into smaller spaces recursively; they are chosen to improve parallelism while maintaining cache efficiency [11].

Thanks to cut dependence analysis, the resultant trapezoids can span iterations of a time loop. Note that the domain which Pochoir operates on are unions of convex polyhedra, which are more general than the hyperrectangular iteration spaces described so far.

#### Applicability

The Cilk Plus framework, which Pochoir uses, is intended to produce optimal scheduling for parallel tasks, and cache-oblivious algorithms may be optimal up to a constant factor, which would be interesting when targeting multiple platforms. Nevertheless, significant speedup can occur with *cache-aware* algorithms, which employ tuning for

<sup>&</sup>lt;sup>4</sup>The Pochoir compiler will also invoke the user's Cilk Plus compiler.

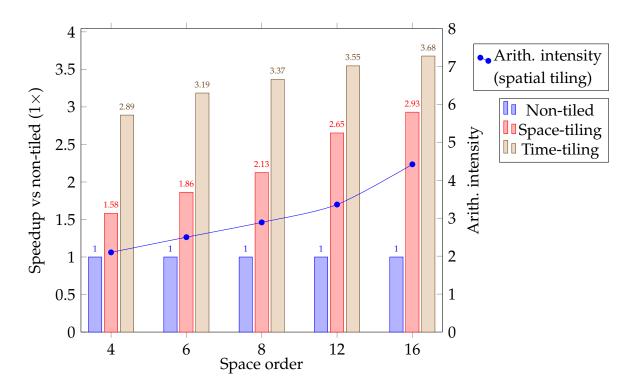

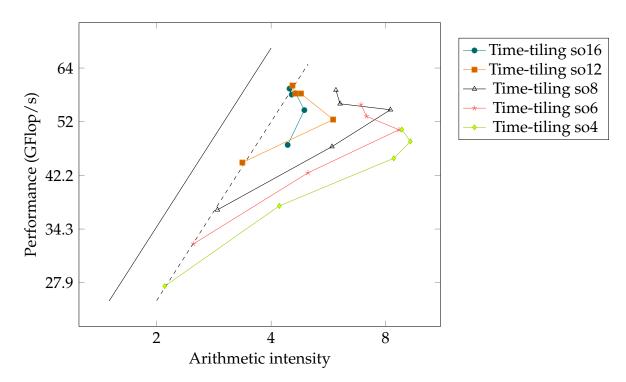

multiple levels of cache [14]. Indeed, due to a difficulty in choosing suitable base case sizes for the interior trapezoids, Pochoir includes an auto-tuner for this purpose. This is especially significant to domain specialists who are experimenting and changing models, or those who are performing stencil computations over large iteration spaces.